### CS3351-DIGITAL PRINCIPLES AND COMPUTER ORGANIZATION

# **UNITICOMBINATIONALCIRCUITS:**

# -Combinational Circuits

- Karnaugh Map Analysis and Design Procedures

- Binary Adder Subtractor

- Decimal Adder

- Magnitude Comparator

- Decoder

- Encoder

www.EnggTree.com

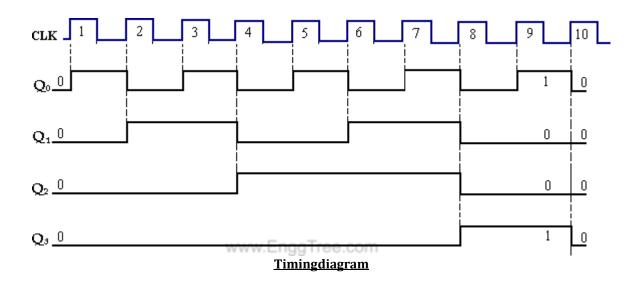

- Multiplexers

- Demultiplexers

# **INTRODUCTION:**

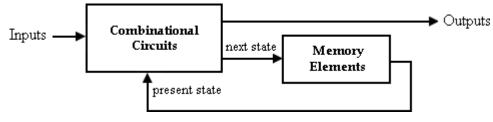

The digital system consists of two types of circuits, namely

- (i) Combinational circuits

- (ii) Sequential circuits

**Combinationalcircuit**consistsoflogicgateswhoseoutputatanytimeisdeter mined from the present combination of inputs. The logic gate is the most basicbuildingblockofcombinationallogic.Thelogicalfunctionperformedbyacomb inationalcircuitisfullydefinedbyasetofBooleanexpressions.

Sequential logic circuit comprises both logic gates and the state of storageelementssuchasflip-

flops. As a consequence, the output of a sequential circuit depends not only on present v alue of inputs but also on the past state of inputs.

Intheprevious chapter, we have discussed binary numbers, codes, Boolean alge braand simplification of Boolean function and logic gates. In this chapter, formulation and analysis of various systematic designs of combinational circuits will be discussed.

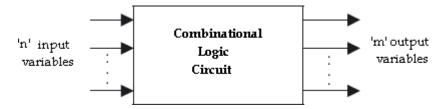

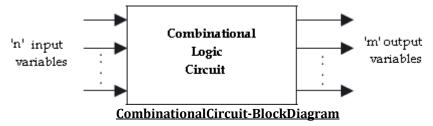

Acombinational circuit consists of input variables, logic gates, and output varia bles. The logic gates accept signals from inputs and output signals are generated according to the logic circuits employed in it. Binary information from the given data transforms to desired output data in this process. Both input and output are obviously the binary signals, *i.e.*, both the input and output signals are of two possible states, logic landlogic 0.

### **Blockdiagramofacombinationallogiccircuit**

For *n* number of input variables to a combinational circuit,  $2^n$  possible combinations of binary input states are possible. For each possible combination, there is one and only one possible output combination. A combinational logic circuit can be described by *m* Boolean functions and each output can be expressed in terms of *n* input variables.

www.EnggTree.com

# **DESIGNPROCEDURE:**

$\label{eq:combinational} Any combinational circuit can be designed by the following steps of design procedure.$

- 1. Theproblemisstated.

- 2. Identifytheinputandoutputvariables.

- 3. The input and output variables are assigned letter symbols.

- 4. Constructionofatruthtabletomeetinput-outputrequirements.

- 5. WritingBooleanexpressionsforvariousoutputvariablesintermsofinp utvariables.

- 6. ThesimplifiedBooleanexpressionisobtainedbyanymethodofminimization —algebraic method,Karnaughmapmethod,ortabulationmethod.

- 7. Alogicdiagramisrealizedfromthesimplifiedbooleanexpressionusinglog icgates.

The following guidelines should be followed while choosing the preferred form for hard ware implementation:

- 1. Theimplementationshouldhavetheminimumnumberofgates, with the gate sused having the minimum number of inputs.

- 2. Thereshouldbeaminimumnumberofinterconnections.

- 3. Limitationonthedrivingcapabilityofthegatesshouldnotbeignored.

# ARITHMETICCIRCUITS-BASICBUILDINGBLOCKS:

Inthissection, we will discuss those combinational logic building blocks that can be used to perform addition and subtraction operations on binary numbers. Additionand subtraction are the two most commonly used arithmetic operations, as the other two, namely multiplication and division, are respectively the processes of repeated addition and repeated subtraction.

The basic building blocks that form the basis of all hardware used to perform the a rithmetic operations on binary numbers are half-adder, full adder, half-subtractor, full-subtractor.

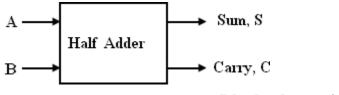

### Half-Adder:

A half-adder is a combinational circuit that can be used to add two binary bits. Ithas two inputs that represent the two bits to be added and two outputs, with oneproducing the SUM output and the other producing the CARRY.

#### **Blockschematicofhalf-adder**

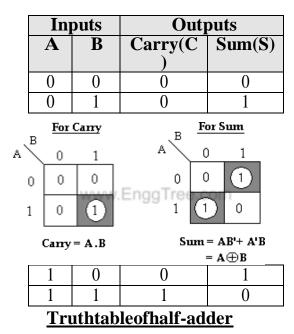

Thetruthtableofahalf-

adder, showing all possible input combinations and the corresponding outputs are shown below.

### K-mapsimplificationforcarryandsum:

TheBooleanexpressionsfortheSUMandCARRYoutputsaregivenbytheequations, Sum,S =A'B+AB'=A $\oplus$ B

### Carry,C=A.B

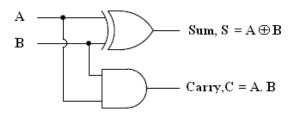

The first one representing the SUM output is that of an EX-

ORgate, the second one representing the CARRY output is that of an AND gate.

The logicdiagram of the half adderis,

### <u>Full-</u>

### Adder:

$\label{eq:2.1} A full add eris a combinational circuit that forms the arithmetic sum of three input bits. It consists of 3 inputs and 2 outputs.$

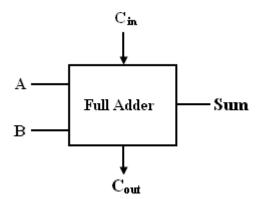

Two of the input variables, represent the significant bits to be added. The thirdinputrepresents the carry from previous lower significant position. The block dia gramofful ladder is given by,

### **Blockschematicoffull-adder**

The full adder circuit overcomes the limitation of the half-adder, which can beused to add two bits only. As there are three input variables, eight different inputcombinations are possible. The truth table is shown below,

TruthTable:

|   | Input<br>s |   | Output<br>s |                 |  |

|---|------------|---|-------------|-----------------|--|

| Α | B Ci<br>n  |   | Sum(S)      | Carry(Co<br>ut) |  |

| 0 | 0          | 0 | 0           | 0               |  |

| 0 | 0          | 1 | 1           | 0               |  |

| 0 | 1          | 0 | 1           | 0               |  |

| 0 | 1          | 1 | 0           | 1               |  |

| 1 | 0          | 0 | 1           | 0               |  |

| 1 | 0          | 1 | 0           | 1               |  |

| 1 | 1          | 0 | 0           | 1               |  |

| 1 | 1          | 1 | 1           | 1               |  |

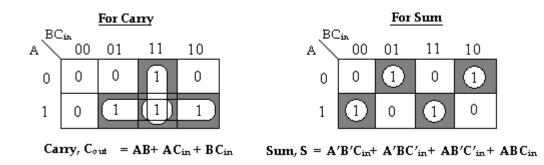

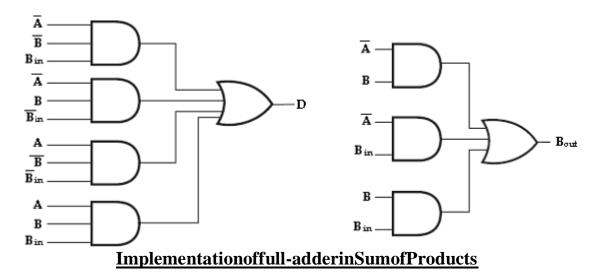

Toderive the simplified Boolean expression from the truth table, the Karnaugh map method is adopted as,

The Boolean expressions for the SUM and CARRY outputs are given by the equations,

```

Sum,S =A'B'Cin+A'BC'in+AB'C'in+ABCin

Carry,Cout =AB+ACin+BCin.

```

Thelogic diagram for the above functions is shown as,

#### Implementationoffull-adderinSumofProducts

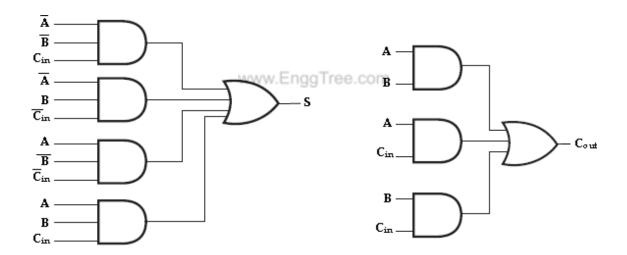

Thelogicdiagram of the full adder can also be implemented with two halfadders and one OR gate. The S output from the second half adder is the exclusive-OR of Cinand the output of the first half-adder, giving

Sum=Cin $\oplus$ (A $\oplus$ B) [x $\oplus$ y=x'y+xy'] =Cin $\oplus$ (A'B+AB') =C'in(A'B+AB')+Cin(A'B+AB')' [(x'y+xy')'=(xy+x'y')] =C'in(A'B+AB')+Cin(AB+A'B')

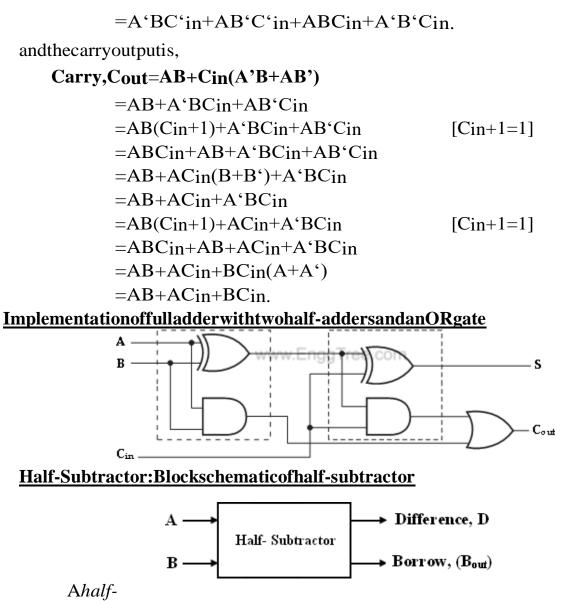

subtractor is a combinational circuit that can be used to subtract one binary digit from an other to produce a DIFFERENCE output and a BORROW output. The BORROW output put here specifies whether a 1 'has been borrowed to perform the subtraction. The trut htable of half-

subtractor, showing all possible input combinations and the corresponding outputs ar eshown below.

| I | nput | Output            |              |  |  |

|---|------|-------------------|--------------|--|--|

| Α | В    | Difference(<br>D) | Borrow(Bout) |  |  |

| 0 | 0    | 0                 | 0            |  |  |

| 0 | 1    | 1                 | 1            |  |  |

| 1 |      | baded from Er     |              |  |  |

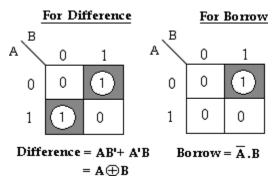

#### K-mapsimplificationforhalfsubtractor:

The Boolean expressions for the DIFFERENCE and BORROW outputs are givenbytheequations,

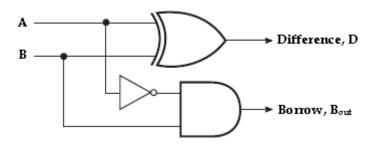

Difference,D= A'B+ AB'=A⊕B Borrow,Bout =A'.B

The first one representing the DIFFERENCE (**D**)output is that of an exclusive-ORgate, the expression for the BORROW output (**Bout**) is that of an AND gate with input Acomplementedbeforeitisfedtothegate.

The logicdiagramofthehalf adderis,

#### LogicImplementationofHalf-Subtractor

Comparing a half-subtractor with a half-adder, we find that the expressions for the SUM and DIFFERENCE outputs are just the same. The expression for BORROW in the case of the half-subtractor is also similar to what we have for CARRY in the case of the half-adder. If the input A, ie., the minuend is Downloaded from EnggTree.comD gate can

beusedtoimplementtheBORROWoutput.

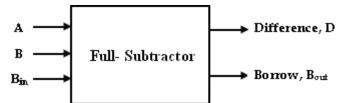

FullSubtractor:

A*fullsubtractor* performs subtraction operation on two bits, a minuend and as ubtra hend, and also takes into consideration whether <u>1</u> has already been borrowed by the previous adjacent lower minuend bit or not.

As a result, there are three bits to be handled at the input of a full subtractor, namely the two bits to be subtracted and a borrow bit designated as Bin. There are twooutputs, namely the DIFFERENCE output Dandthe BORROW output Bo. The BORROW output bit tells whether the minuend bit

needs to borrow a 1' from the nextpossible higher minuend bit.

### **Block schematicof full-adder**

Thetruthtableforfull-subtractoris,

|   | Input<br>s | www.Eng | gTree.com <mark>Out</mark> j<br>s |     |

|---|------------|---------|-----------------------------------|-----|

| Α | B          | Bi      | <b>Difference</b> ( <b>D</b>      |     |

|   |            | n       | )                                 | ut) |

| 0 | 0          | 0       | 0                                 | 0   |

| 0 | 0          | 1       | 1                                 | 1   |

| 0 | 1          | 0       | 1                                 | 1   |

| 0 | 1          | 1       | 0                                 | 1   |

| 1 | 0          | 0       | 1                                 | 0   |

| 1 | 0          | 1       | 0                                 | 0   |

| 1 | 1          | 0       | 0                                 | 0   |

| 1 | 1          | 1       | 1                                 | 1   |

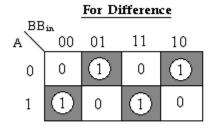

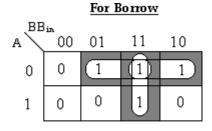

### K-map simplification for full-subtractor:

Difference,  $D = A'B'B_{in} + A'BB'_{in} + AB'B'_{in} + ABB_{in}$

$Borrow, B_{out} = A'B + A'B_{in} + BB_{in}$

The Boolean expressions for the DIFFERENCE and BORROW outputs are given by the equations,

#### Difference,D =A'B'Bin+A'BB'in+AB'B'in+ABBin

#### Borrow,Bout =A'B+A'Cin+BBin.

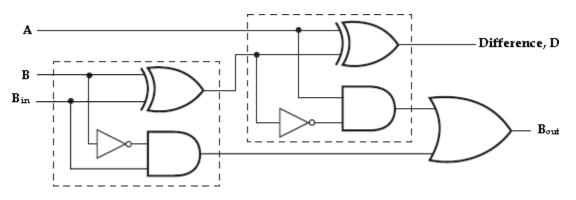

Thelogic diagram for the above functions is shown as,

The logic diagram of the full-subtractor can also be implemented with two half-

subtractors and one OR gate. The difference, Doutput from the second half subtractor is the exclusive-OR of Bin and the output of the first half-subtractor, giving

**Difference**,  $D = Bin \oplus (A \oplus B)$  $[x \oplus y = x'y + xy']$ =**B**in(A'B+AB') =B'in(A'B+AB')+Bin(A'B+AB')' [(x'y+xy')'=(xy+x'y')]=B'in(A'B+AB')+Bin(AB+A'B')= A'BB'in + AB'B'in + ABBin + A'B'Bin.and the borrow output is, Borrow,Bout=A'B+Bin(A'B+AB')'[(x'y+xy')'=(xy+x'y')] =A'B+Bin(AB+A'B')= A'B+ABBin+A'B'Bin=A'B(Bin+1)+ABBin+A'B'Bin[Cin+1=1]=A'BBin+A'B+ABBin+A'B'Bin = A'B + BBin(A+A') + A'B'Bin[A+A'=1]=A'B+BBin+A'B'Bin =A'B(Bin+1)+BBin+A'B'Bin[Cin+1=1]=A'BBin+A'B+BBin+A'B'Bin Downloaded from EnggTree.com

Therefore,

we can implement full-subtractor using two half-subtractors and OR gate as,

#### Implementationoffull-subtractorwithtwohalfsubtractorsandanORgate

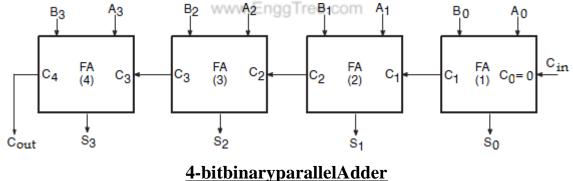

### Four -bit BinaryAdder(ParallelAdder):

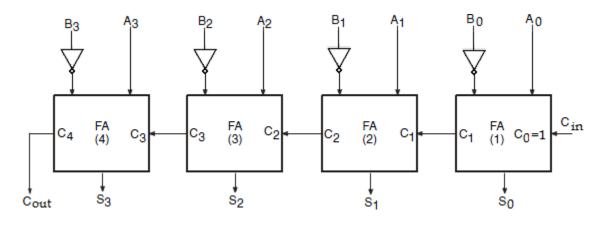

The4-bitbinaryadderusingfulladdercircuitsiscapableofaddingtwo4bitnumbersresulting ina4-bit sumanda carry output as showninfigure below.

+-bitbillar y par allen Auder

Since all the bits of augendand addendare fed into the adder circuits simultaneous sly and the additions in each position are taking place at the same time, this circuit is known as parallel adder.

Letthe4-

bitwordstobeaddedberepresentedby,A3A2A1A0=1111andB3B 2B1B0=0011.

Significant place  $4\ 3\ 2\ 1$ Input carry  $1\ 1\ 1\ 0$ Augend word A :  $1\ 1\ 1\ 1$ Addend word B :  $0\ 0\ 1\ 1$   $1\ 0\ 0\ 1\ 0 \leftarrow Sum$   $\uparrow$ Output Carry

Thebitsareaddedwithfulladders,startingfromtheleastsignificantposition,to formthesumitandcarrybit.TheinputcarryC0intheleastsignificantpositionmustbe 0. The carry output of the lower order stage is connected to the carry input of the nexthigherorderstage.Hencethistypeofadderiscalledripple-carryadder.

In the least significant stage, A0, B0 and C0 (which is 0) are added resulting insumS0andcarryC1.ThiscarryC1becomesthecarryinputtothesecond stage.Similarly in the second stage, A1, B1 and C1 are added resulting in sum S1 and carry C2, in the third stage, A2, B2 and C2 are added resulting in sum S2 and carry C3, in the thirdstage, A3, B3 and C3 are added resulting in sum S3 and C4, which is the output carry.Thusthe circuitresultsin a sum(S3S2S1S0) and acarry output(Cout).

Though the parallel binary adder is said to generate its output immediately after the inputs are applied, its speed of operation is limited by the carry propagation delaythrough all stages. However, there are several methods to reduce this delay.

One of the methods of speeding up this process is look-ahead carry additionwhicheliminatestheripple-carrydelay.

### **BinarySubtractor(ParallelSubtractor):**

The subtraction of unsigned binary numbers can be done most conveniently bymeans of complements. The subtraction A-B can be done by taking the 2's complementofBandaddingittoA.The2'scomplementcanbeobtainedbytakingthe1 'scomplementandadding1totheleastsignificantpairofbits.

The 1`s complement can be implemented with inverters and a 1 can be added to the sum through the input carry.

The circuit for subtracting A-B consists of an adder with inverters placed between each data input B and the corresponding input of the full adder. The input carry C0 must be equal to 1 when performing subtraction. The operation thus perf or med becomes A, plus the 1's complement of B, plus 1. This is equal to A plus the 2's complement of B.

#### **<u>4-bitParallelSubtractor</u>**

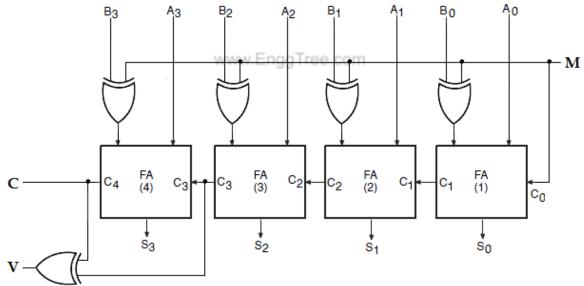

#### **<u>4-Bit ParallelAdder/Subtractor:</u>**

The addition and subtraction operation can be combined into one circuit withone common binary adder. This is done by including an exclusive-OR

$gate\ with\ each full adder. A 4-bit adder Subtractor circuit is shown below.$

$\label{eq:model} The model input M controls the operation. When M=0, the circuit is an adder and when M=1, the circuit becomes a Subtractor. Each exclusive-$

ORgatereceivesinputMand one of the inputs of B. When M=0, we have B 0= B. The full adders receive

thevalueofB,theinputcarryis0,andthecircuitperformsAplusB.WhenM=1,wehave B 1=B' and C0=1. The B inputs are all complemented and a 1 is added through theinput carry. The circuit performs the operation A plus the 2's complement of B. Theexclusive-ORwithoutputVisfordetectinganoverflow. **DecimalAdder(BCDAdder):**

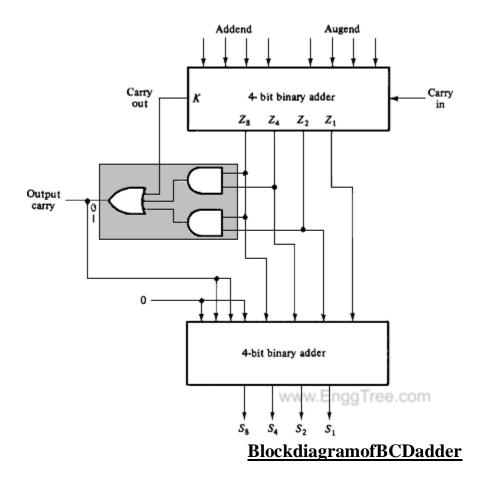

The digital system handles the decimal number in the form of binary Downloaded from EnggTree.com coded decimal numbers (BCD). ABCD adder is a circuit that adds two BCD bits and produces a sum digital so in BCD.

Consider the arithmetic addition of two decimal digits in BCD, together with an input carry from a previous stage. Since each input digit does not exceed 9, the output sum cannot be greater than 9+9+1 = 19; the 1 is the sum being an input carry. The adder will form the sum in binary and produce are sult that ranges from 0 through 19.

These binary numbers are labeled by symbols K, Z8, Z4, Z2, Z1, K is the carry.

The column sunder the binary sum list the binary values that appear in the outputs of the 4-bit bit binary adder. The output sum of the two decimal digits must be represented in BCD.

|   | Bin | ary       | Sun | n         |   | BCD Sum   |   |      |    |         |

|---|-----|-----------|-----|-----------|---|-----------|---|------|----|---------|

| K |     | <b>Z4</b> | Z2  | <b>Z1</b> | С | <b>S8</b> |   | S2 S | 51 | Decimal |

|   | 8   |           | 0   |           |   |           | 4 |      |    |         |

| 0 | 0   | 0         | 0   | 0         | 0 | 0         | 0 | 0    | 0  | 0       |

| 0 | 0   | 0         | 0   | 1         | 0 | 0         | 0 | 0    | 1  | 1       |

| 0 | 0   | 0         | 1   | 0         | 0 | 0         | 0 | 1    | 0  | _2      |

| 0 | 0   | 0         | 1   | 1         | 0 | 0         | 0 | 1    | 1  | 3       |

| 0 | 0   | 1         | 0   | 0         | 0 | 0         | 1 | 0    | 0  | 4       |

| 0 | 0   | 1         | 0   | 1         | 0 | 0         | 1 | 0    | 1  | 5       |

| 0 | 0   | 1         | 1   | 0         | 0 | 0         | 1 | 1    | 0  | 6       |

| 0 | 0   | 1         | 1   | 1         | 0 | 0         | 1 | 1    | 1  | 7       |

| 0 | 1   | 0         | 0   | 0         | 0 | 1         | 0 | 0    | 0  | 8       |

| 0 | 1   | 0         | 0   | 1         | 0 | 1         | 0 | 0    | 1  | 9       |

| 0 | 1   | 0         | 1   | 0         | 1 | 0         | 0 | 0    | 0  | 10      |

| 0 | 1   | 0         | 1   | 1         | 1 | 0         | 0 | 0    | 1  | 11      |

| 0 | 1   | 1         | 0   | 0         | 1 | 0         | 0 | 1    | 0  | 12      |

| 0 | 1   | 1         | 0   | 1         | 1 | 0         | 0 | 1    | 1  | 13      |

| 0 | 1   | 1         | 1   | 0         | 1 | 0         | 1 | 0    | 0  | 14      |

| 0 | 1   | 1         | 1   | 1         | 1 | 0         | 1 | 0    | 1  | 15      |

| 1 | 0   | 0         | 0   | 0         | 1 | 0         | 1 | 1    | 0  | 16      |

| 1 | 0   | 0         | 0   | 1         | 1 | 0         | 1 | 1    | 1  | 17      |

| 1 | 0   | 0         | 1   | 0         | 1 | 1         | 0 | 0    | 0  | 18      |

| 1 | 0   | 0         | 1   | 1         | 1 | 1         | 0 | 0    | 1  | 19      |

In examining the contents of the table, it is apparent that when the binary sum isequal to or less than 1001, the corresponding BCD number is identical, and Downloaded from EnggTree.com

therefore noconversionis needed. When the binarysum is greaterthan 9(1001), weobtain anon-

validBCDrepresentation.Theadditionofbinary6(0110)tothebinarysumconvertsittoth ecorrectBCDrepresentationandalsoproducesanoutputcarryasrequired.

Thelogiccircuittodetectsumgreaterthan9canbedeterminedbysimplifyingthebooleanexpressionofthegiventruthtable.

|                       | Inj            | puts       |                | Output |   |

|-----------------------|----------------|------------|----------------|--------|---|

| <b>S</b> <sub>3</sub> | $\mathbf{S}_2$ | <b>S</b> 1 | S <sub>0</sub> | Y      |   |

| 0                     | 0              | 0          | 0              | 0      |   |

| 0                     | 0              | 0          | 1              | 0      |   |

| 0                     | 0              | 1          | 0              | 0      |   |

| 0                     | 0              | 1          | 1              | 0      |   |

| 0                     | 1              | 0          | 0              | 0      |   |

| 0                     | 1              | 0          | 1              | 0      |   |

| 0                     | 1              | 1          | 0              | 0      |   |

| 0                     | 1              | 1          | 1              | 0      |   |

| 1                     | 0              | 0          | 0              | 0      |   |

| 1                     | 0              | 0          | 1              | 0      |   |

| 1                     | 0              | 1          | 0              | 1      | W |

| 1                     | 0              | 1          | 1              | 1      |   |

| 1                     | 1              | 0          | 0              | 1      |   |

| 1                     | 1              | 0          | 1              | 1      |   |

| 1                     | 1              | 1          | 0              | 1      |   |

| 1                     | 1              | 1          | 1              | 1      |   |

| S1       | So |    |    |    |

|----------|----|----|----|----|

| S3 S2 S1 | 00 | 01 | 11 | 10 |

| 00       | 0  | 0  | 0  | 0  |

| 01       | 0  | 0  | 0  | 0  |

| 11       | 1  | 1  | 1  | 1  |

| 10       | 0  | 0  | 1  | 1  |

$\mathsf{vww}.\mathsf{Eng}Y = \mathbf{S}_3\mathbf{S}_2 + \mathbf{S}_3\mathbf{S}_1$

ToimplementBCDadder werequire:

- 4-bitbinaryadderforinitialaddition

- Logiccircuittodetectsumgreaterthan9and

- Onemore4-bitaddertoadd01102inthesumifthesumisgreaterthan9orcarryis1.

The twodecimal digits, togetherwith the inputcarry, are firstadded in the top4-bit binary adder to provide the binary sum. When the output carry is equal to zero,nothing is added to the binarysum. When it equal to one, binary0110 is added to the binary sum through the bottom 4-bit adder. The output carry generated from thebottom adder can be ignored, since it supplies information already available at theoutputcarryterminal. Theoutputcarryfromonestagemust beconnected to the input carry of the extension.

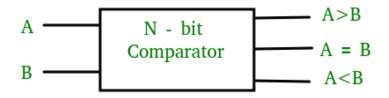

### **MAGNITUDECOMPARATOR:**

A *magnitude comparator* is a combinational circuit that compares two givennumbers(AandB)anddetermineswhetheroneisequalto,lessthanorgreatertha ntheother.Theoutputisintheformofthreebinaryvariables

#### **Blockdiagramofn-Bit magnitudecomparator**

representing the conditions A=B, A>B and A<B, if A and B are the two numbers being compared.

For comparison of two *n*-bit numbers, the classical method to achieve the Boolean expressions requires a truth table of  $2^{2n}$  entries and becomes too lengthy and cumbersome.

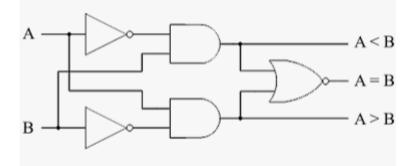

### **1-Bit Magnitude Comparator:**

A comparator used to compare two bits is called a single-bit comparator. It consists of two inputs each for two single-bit numbers and three outputs to generate less than, equal to, and greater than between two binary numbers.

The truth table for a 1-bit comparator is given below:

| Α | В | A <b< th=""><th>A=B</th><th>A&gt;B</th></b<> | A=B | A>B |

|---|---|----------------------------------------------|-----|-----|

| 0 | 0 | 0                                            | 1   | 0   |

| 0 | 1 | 1                                            | 0   | 0   |

| 1 | 0 | 0                                            | 0   | 1   |

| 1 | 1 | 0                                            | 1   | 0   |

www.EnggTree.com

From the above truth table logical expressions for each output can be expressed as follows:

A>B: AB'

A<B: A'B

A=B: A'B' + AB

From the above expressions we can derive the following formula:

```

(A < B) + (A > B) = A'B + AB'

<u>Taking complement both sides</u>

((A < B) + (A > B))' = (A'B + AB')'

((A < B) + (A > B))' = (A'B)' (AB')'

((A < B) + (A > B))' = (A + B') (A' + B)

((A < B) + (A > B))' = (AA' + AB + A'B' + BB')

" = (AB + A'B')

Thus,

((A < B) + (A > B))' = (A = B)

```

By using these Boolean expressions, we can implement a logic circuit for this comparator as given below:

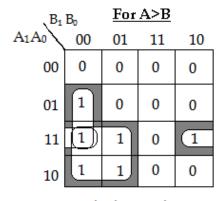

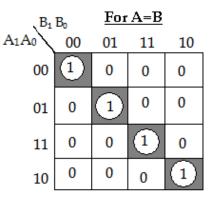

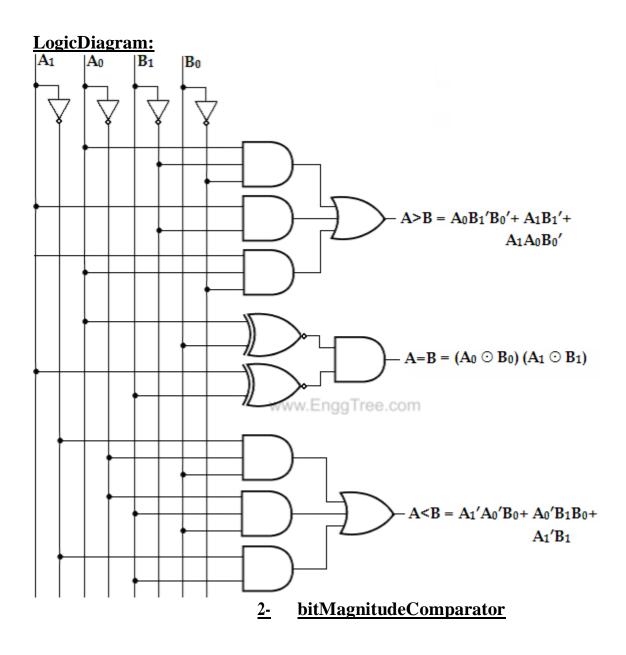

#### **<u>2-bitMagnitudeComparator:</u>**

Thetruthtableof2-bitcomparatorisgivenintablebelow-

Truthtable:

|        | Ing |   |                    |     | Outputs |                   |

|--------|-----|---|--------------------|-----|---------|-------------------|

| A<br>3 | A2  |   | ww. <b>A0</b> ggTi | A>B | A=B     | A <b< th=""></b<> |

| 0      | 0   | 0 | 0                  | 0   | 1       | 0                 |

| 0      | 0   | 0 | 1                  | 0   | 0       | 1                 |

| 0      | 0   | 1 | 0                  | 0   | 0       | 1                 |

| 0      | 0   | 1 | 1                  | 0   | 0       | 1                 |

| 0      | 1   | 0 | 0                  | 1   | 0       | 0                 |

| 0      | 1   | 0 | 1                  | 0   | 1       | 0                 |

| 0      | 1   | 1 | 0                  | 0   | 0       | 1                 |

| 0      | 1   | 1 | 1                  | 0   | 0       | 1                 |

| 1      | 0   | 0 | 0                  | 1   | 0       | 0                 |

| 1      | 0   | 0 | 1                  | 1   | 0       | 0                 |

| 1      | 0   | 1 | 0                  | 0   | 1       | 0                 |

| 1      | 0   | 1 | 1                  | 0   | 0       | 1                 |

| 1      | 1   | 0 | 0                  | 1   | 0       | 0                 |

| 1      | 1   | 0 | 1                  | 1   | 0       | 0                 |

| 1      | 1   | 1 | 0                  | 1   | 0       | 0                 |

| 1      | 1   | 1 | 1                  | 0   | 1       | 0                 |

K-mapSimplification:

$\mathbf{A}{>}\mathbf{B}=\mathbf{A}_{0}\mathbf{B}_{1}{'}\mathbf{B}_{0}{'}{+}\ \mathbf{A}_{1}\mathbf{B}_{1}{'}{+}\ \mathbf{A}_{1}\mathbf{A}_{0}\mathbf{B}_{0}{'}$

$\begin{aligned} \mathbf{A} &= \mathbf{B} = \mathbf{A}_{1}' \mathbf{A}_{0}' \mathbf{B}_{1}' \mathbf{B}_{0}' + \mathbf{A}_{1}' \mathbf{A}_{0} \mathbf{B}_{1}' \mathbf{B}_{0} + \\ \mathbf{A}_{1} \mathbf{A}_{0} \mathbf{B}_{1} \mathbf{B}_{0} + \mathbf{A}_{1} \mathbf{A}_{0}' \mathbf{B}_{1} \mathbf{B}_{0}' \\ &= \mathbf{A}_{1}' \mathbf{B}_{1}' \left( \mathbf{A}_{0}' \mathbf{B}_{0}' + \mathbf{A}_{0} \mathbf{B}_{0} \right) + \mathbf{A}_{1} \mathbf{B}_{1} \left( \mathbf{A}_{0} \mathbf{B}_{0} + \mathbf{A}_{0}' \mathbf{B}_{0}' \right) \\ &= \left( \mathbf{A}_{0} \odot \mathbf{B}_{0} \right) \left( \mathbf{A}_{1} \odot \mathbf{B}_{1} \right) \end{aligned}$

| р       | р     | For A <b< th=""></b<> |    |         |  |  |  |  |

|---------|-------|-----------------------|----|---------|--|--|--|--|

| A1A0 B1 | D0 00 | 01                    | 11 | 10      |  |  |  |  |

| 00      | ₩.E   | 1                     | 1  | 2<br>Dm |  |  |  |  |

| 01      | 0     | 0                     | 1  | 1       |  |  |  |  |

| 11      | 0     | 0                     | 0  | 0       |  |  |  |  |

| 10      | 0     | 0                     | 1  | 0       |  |  |  |  |

$\mathbf{A}{\boldsymbol{<}}\mathbf{B} = \mathbf{A}_{1}{^{\prime}}\mathbf{A}_{0}{^{\prime}}\mathbf{B}_{0}{\boldsymbol{+}} + \mathbf{A}_{0}{^{\prime}}\mathbf{B}_{1}\mathbf{B}_{0}{\boldsymbol{+}} + \mathbf{A}_{1}{^{\prime}}\mathbf{B}_{1}$

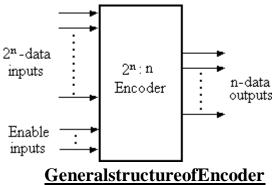

#### **ENCODERS:**

An encoder is a digital circuit that performs the inverse operation of a decoder.Hence,theoppositeofthedecodingprocessiscalledencoding.Anencoderis acombinational circuit that converts binary information from  $2^n$  input lines to a maxim umof\_n'unique output lines.

Thegeneralstructureofencodercircuitis-

It has  $2^n$  input lines, only one which 1 is active at any time and \_n' output lines. Itencodes one of the active inputs to a coded binary output with \_n' bits. In an encoder, the number of output sisless than the number of inputs.

#### **Octal-to-BinaryEncoder:**

It has eight inputs (one for each of the octal digits) and the three outputs that generate the corresponding binary number. It is assumed that only one input has avalueof1atanygiventime.

|   | Inputs |   |   |   |   |   |   |   | Outpu | ts |

|---|--------|---|---|---|---|---|---|---|-------|----|

| D | D      | D | D | D | D | D | D | Α | B     | С  |

| 0 | 1      | 2 | 3 | 4 | 5 | 6 | 7 |   |       |    |

| 1 | 0      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 0  |

| 0 | 1      | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0     | 1  |

| 0 | 0      | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1     | 0  |

| 0 | 0      | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1     | 1  |

| 0 | 0      | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 0     | 0  |

| 0 | 0      | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0     | 1  |

| 0 | 0      | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1     | 0  |

| 0 | 0      | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1     | 1  |

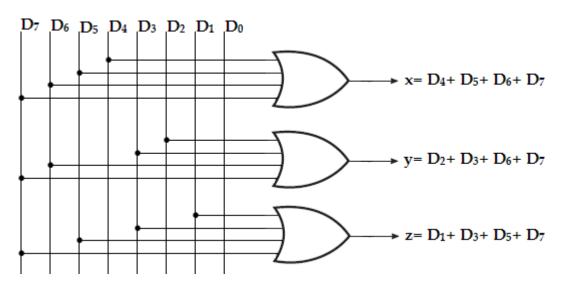

The encoder can be implemented with OR gates whose inputs are determineddirectly from the truth table. Output z is equal to 1, when the input Downloaded from EnggTree.com

octaldigitis1or3or5or7.Outputyis1foroctaldigits2,3,6,or7andtheoutputis1fordigits4,5,6or7.TheseconditionscanbeexpressedbythefollowingoutputBooleanfunctions:

# z=D1+D3+D5+D7 y=D2+D3+D6+D7 x=D4+D5+D6+D7

The encoder can be implemented with three OR gates. The encoder defined in the below table, has the limitation that only one input can be active at any given time. If two inputs are active simultaneously, the output produces an undefined combinatio n.

For eg., if D3 and D6 are 1 simultaneously, the output of the encoder may be 111. This does not represent either D6 or D3. To resolve this problem, encoder circuits must establish an input priority to ensure that only one input is encoded. If we establish a higher priority for inputs with higher subscript numbers and if D3and D6are 1 at thesame time, the output will be 110 because D6hashigher priority than D3.ggTree.com

### **Octal-to-BinaryEncoder**

Another problem in the octal-to-binary encoder is that an output with all 0's isgenerated when all the inputs are 0; this output is same as when D0is equal to 1. The discrepancy can be resolved by providing one more output to indicate that at least one input is equal to 1.

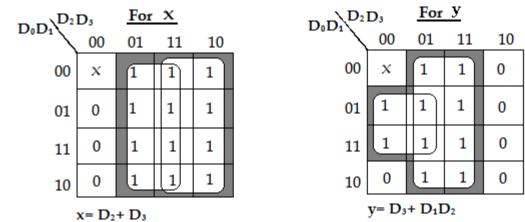

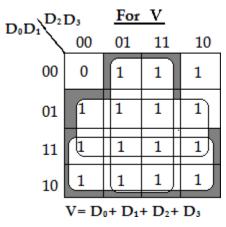

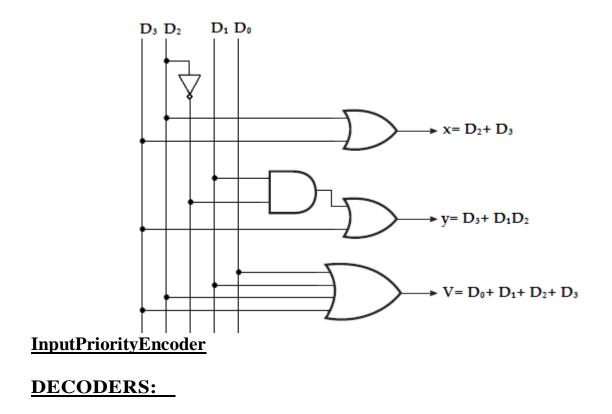

### **PriorityEncoder:**

A priority encoder is an encoder circuit that includes the priority function.

In priority encoder, if two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence.

In addition to the two outputs x and y, the circuit has a third output, V (valid bitindicator). It is set to 1 whenoneormore inputs are equal to 1. If all inputs are 0, there is novalid input and V is equal to 0. The higher the subscript number, higher the priority of the input D3, has the highest priority. So, regardless of the values of the other inputs, when D3 is 1, the output for xy is 11.

$D_2$  has the next priority level. The output is 10, if  $D_2 = 1$  provided  $D_3 = 0$ . The output for  $rD_1$  is generated only if higher priority inputs are 0, and so on down the priority levels. **Truthtable:**

|   | _ | put<br>s        | Outputs |       |   |   |

|---|---|-----------------|---------|-------|---|---|

| D | D | D               | D       | X     | У | V |

| 0 | 1 | ww <b>2</b> r.E | ng3Tre  | e.com |   |   |

| 0 | 0 | 0               | 0       | Х     | Х | 0 |

| 1 | 0 | 0               | 0       | 0     | 0 | 1 |

| X | 1 | 0               | 0       | 0     | 1 | 1 |

| X | Х | 1               | 0       | 1     | 0 | 1 |

| X | Х | X               | 1       | 1     | 1 | 1 |

Although the above table has only five rows, when each don't care condition is replaced first by 0 and then by 1, we obtain all 16 possible input combinations.

Forexample,thethirdrowinthetablewithX100representsminterms0100and1100.T hedon'tcareconditionis replacedby0and 1asshown in thetable below.

### ModifiedTruthtable:

|               | _             | put<br>s      |               | (      | Dutput | ts |

|---------------|---------------|---------------|---------------|--------|--------|----|

| D             | D             | D             | D             | X      | у      | V  |

| <b>0</b><br>0 | <b>1</b><br>0 | <b>2</b><br>0 | <b>3</b><br>0 | v      | V      | 0  |

| 1             | 0             | 0             | 0             | x<br>0 | x<br>0 | 1  |

| $\frac{1}{0}$ | 1             | 0             | 0             | 0      | 0      | 1  |

| 1             | 1             | 0             | 0             | 0      | 1      | 1  |

| 0             | 0             | 1             | 0             |        |        |    |

| 0             | 1             | 1             | 0             |        | 0      |    |

| 1             | 0             | 1             | 0             | 1      | 0      | 1  |

| 1             | 1             | 1             | 0             |        |        |    |

| 0             | 0             | 0             | 1             |        |        |    |

| 0             | 0             | 1             | 1             |        |        |    |

| 0             | 1             | 0             | 1             |        |        |    |

| 0             | 1             | 1             | 1             | 1      | 1      | 1  |

| 1             | 0             | 0             | 1             |        |        |    |

| 1             | 0             | 1             | 1             |        |        |    |

| 1             | 1             | ww0.E         | nggTre        | e.com  | 1      |    |

| 1             | 1             | 1             | 1             |        |        |    |

K-mapSimplification:

The priority encoder is implemented according to the above Boolean functions.

www.EnggTree.com

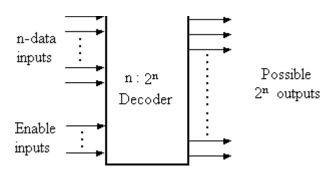

A decoder is a combinational circuit that converts binary information from

\_n'inputlinestoamaximumof\_2n'uniqueoutputlines.Thegeneralstructureofdec odercircuitis-

### **Generalstructureofdecoder**

The encoded information is presented as \_n'input sproducing  $2^{n}$  'possible out puts. The  $2^{n}$  output values are from 0 through  $2^{n}$ -1. A decoder is provided with enable inputs to activate decoded output based on data inputs. When any one enable input is unasserted, all outputs of decoder are disabled.

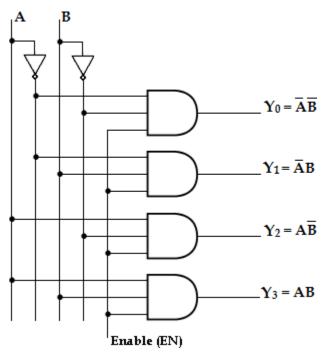

#### **BinaryDecoder**(2to4decoder):

A binary decoder has \_n' bit binary input and a one activated output out Downloaded from EnggTree.com

of  $2^{n}$  outputs. A binary decoder is used when it is necessary to activate exactly one of  $2^{n}$  outputs based on ann-bit input value.

#### 2-to-4Linedecoder

www.EnggTree.com

Here the 2 inputs are decoded into 4 outputs, each output representing one of the minter ms of the two input variables.

| I     | Output<br>s |   |   |   |   |   |

|-------|-------------|---|---|---|---|---|

| Enabl | Α           | В | Y | Y | Y | Y |

| e     |             |   | 3 | 2 | 1 | 0 |

| 0     | X           | Х | 0 | 0 | 0 | 0 |

| 1     | 0           | 0 | 0 | 0 | 0 | 1 |

| 1     | 0           | 1 | 0 | 0 | 1 | 0 |

| 1     | 1           | 0 | 0 | 1 | 0 | 0 |

| 1     | 1           | 1 | 1 | 0 | 0 | 0 |

Asshowninthetruthtable,ifenableinputis1(EN=1)onlyoneoftheoutputs(Y0-Y3),isactiveforagiveninput.

TheoutputY0isactive,ie.,Y0=1wheninputs

A=B=0,Y1isactivewheninputs,

A=0andB=1,

```

Y2isactive,wheninputA=1andB=0,

```

Y3isactive,

wheninputsA=B=1.

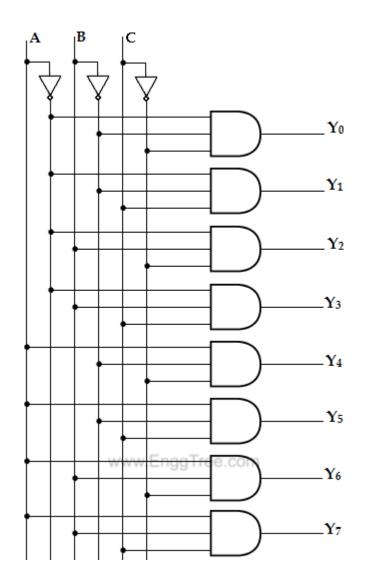

#### 3 to-8LineDecoder:

A3-to-8linedecoderhasthreeinputs(A,B,C)andeightoutputs(Y0-Y7).Basedonthe3inputsoneoftheeightoutputsisselected.

Thethreeinputsaredecodedintoeightoutputs, eachoutputrepresenting one of the minterms of the 3-input variables. This decoder is used for binary-to-octal conversion. The input variables may represent a binary number and the outputs will re present the eight digits in the octal number system. The output variables are mutually exclusive because only one output can be equal to 1 at any one time. The output line whose value is equal to 1 represents the mintermequivalent of the binary ynumber present ly available in the input lines.

| Input<br>s |   |   | Output<br>s |   |        |   |   |   |   |   |

|------------|---|---|-------------|---|--------|---|---|---|---|---|

| Α          | B | С | Ŷ           | Y | Y      | Y | Y | Y | Y | Y |

|            |   |   | 0           | 1 | 2      | 3 | 4 | 5 | 6 | 7 |

| 0          | 0 | 0 | 1           | 0 | 0      | 0 | 0 | 0 | 0 | 0 |

| 0          | 0 | 1 | 0           | 1 | 0      | 0 | 0 | 0 | 0 | 0 |

| 0          | 1 | 0 | 0           | 0 | ginee. | 0 | 0 | 0 | 0 | 0 |

| 0          | 1 | 1 | 0           | 0 | 0      | 1 | 0 | 0 | 0 | 0 |

| 1          | 0 | 0 | 0           | 0 | 0      | 0 | 1 | 0 | 0 | 0 |

| 1          | 0 | 1 | 0           | 0 | 0      | 0 | 0 | 1 | 0 | 0 |

| 1          | 1 | 0 | 0           | 0 | 0      | 0 | 0 | 0 | 1 | 0 |

| 1          | 1 | 1 | 0           | 0 | 0      | 0 | 0 | 0 | 0 | 1 |

### **3-to-8linedecoder**

### **BCDto7-SegmentDisplayDecoder:**

A seven-segment display isnormally usedfordisplaying any one of the decimaldigits,0through9.ABCD-to-

seven segment de coder accepts a decimal digitin BCD and generates the corresponding seven-segment code.

$$\begin{bmatrix} a \\ f \\ g \end{bmatrix} b$$

$$e \begin{bmatrix} d \\ d \end{bmatrix} c$$

Eachsegmentismadeupofamaterialthatemitslightwhencurrentispassedthrou ghit. Thesegments activated during each digit displayaret abulated as—

| Dig<br>it | Displa<br>y            | Segments<br>Activated |

|-----------|------------------------|-----------------------|

| 0         | <br>f b<br>e c         | a,b,c, d,e,f          |

| 1         |                        | b,c                   |

| 2         | www.Engg               | a, b, d, e, g         |

| 3         | <br><br>               | a, b,c,d,g            |

| 4         | f g b                  | b,c,f, g              |

| 5         | a<br>f <u>g</u><br>d c | a,c,d,f,g             |

| - |                                                                                             |                 |

|---|---------------------------------------------------------------------------------------------|-----------------|

| 6 | f g<br>e c                                                                                  | a,c,d,e,f,g     |

| 7 | a<br>b<br>c                                                                                 | a,b,c           |

| 8 | $\begin{array}{c} a \\ f \\ g \\ e \\ d \end{array} = \begin{bmatrix} a \\ c \end{bmatrix}$ | a, b,c,d,e,f, g |

| 9 | f g b                                                                                       | a,b,c,d,f,g     |

# Truthtable:

|           | BCDcode |   |   | 7-<br>Segmentcode |   |   |   |   |   |   |   |

|-----------|---------|---|---|-------------------|---|---|---|---|---|---|---|

| Digi<br>t | Α       | В | С | D                 | a | b | С | d | e | f | g |

| 0         | 0       | 0 | 0 | 0                 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 1         | 0       | 0 | 0 | 1                 | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 2         | 0       | 0 | 1 | 0                 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 3         | 0       | 0 | 1 | 1                 | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 4         | 0       | 1 | 0 | 0                 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5         | 0       | 1 | 0 | 1                 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 6         | 0       | 1 | 1 | 0                 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 7         | 0       | 1 | 1 | 1                 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 8         | 1       | 0 | 0 | 0                 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 9         | 1       | 0 | 0 | 1                 | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

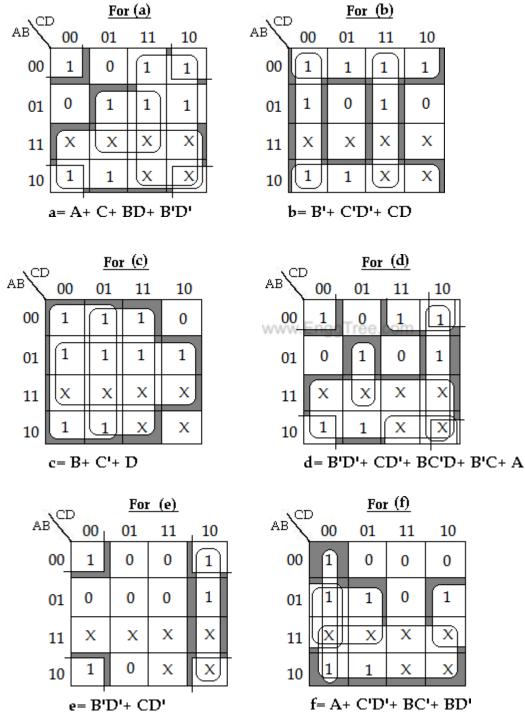

### **K-mapSimplification:**

f = A + C'D' + BC' + BD'

### **BCDto7-segmentdisplaydecoder**

### **Applicationsofdecoders:**

- 1. Decodersareusedincountersystem.

- 2. Theyareusedinanalogtodigitalconverter.

- 3. Decoderoutputscanbeusedtodriveadisplaysystem

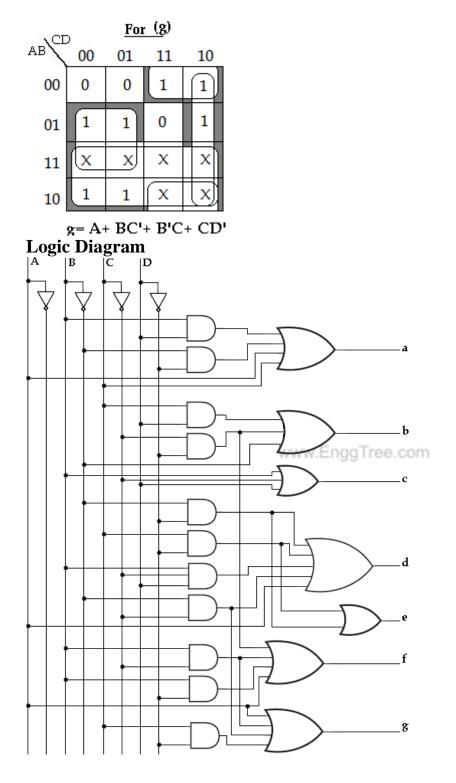

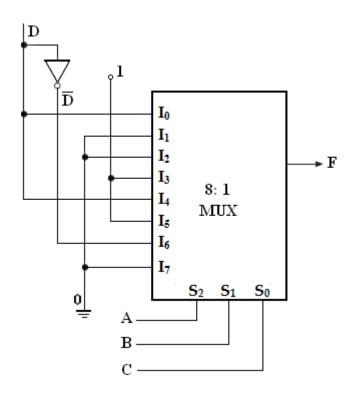

#### MULTIPLEXER:(DataSelector)

A *multiplexer* or *MUX*, is a combinational circuit with more than one input

line, one output line and more than one selection line. A multiple xerse lects binary infor mation present from one of many input lines, depending upon the logic status of the selection inputs, and routes it to the output line. Normally, there are  $2^n$  input lines and n selection lines whose bit combinations determine which input is selected. The multiple xerisoften labeled as MUX in block diagrams.

A multiplexer is also called a **data selector**, since it selects one of many inputsandsteersthebinaryinformation theoutputline.

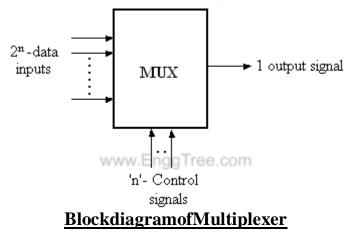

#### <u>2-to-1-lineMultiplexer</u>:

The circuit has two data input lines, one output line and one selection line, S. When S = 0, the upper AND gate is enabled and I (has a path to the output.

When S=1,thelowerAND gate is enabled and I1 has a path to the output.

The multiple xeracts like an electronic switch that selects one of the two sources.

#### **Truthtable:**

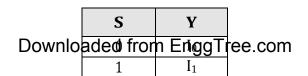

#### 4-to-1-lineMultiplexer:

A 4-to-1-line multiplexer has four  $(2^n)$  input lines, two (n) select lines and oneoutput line. It is the multiplexer consisting of four input channels and information of one of the channels can be selected and transmitted to an output line according to theselect inputs combinations. Selection of one of the four input channel is possible by twoselectioninputs.

EachofthefourinputsI0throughI3, is applied to one inputofAND gate. Selection lines S1 and S0 are decoded to select a particular AND gate. The outputs of the AND gate are applied to a single OR gate that provides the 1-line output.

#### **4-to-1-LineMultiplexer**

### **Functiontable:**

| <b>S1</b> | <b>S0</b> | Y  |

|-----------|-----------|----|

| 0         | 0         | IO |

| 0         | 1         | I1 |

| 1         | 0         | I2 |

| 1         | 1         | I3 |

To demonstrate the circuit operation, consider the case when  $S_1S_0=10$ . The ANDgateassociated with input I2 has two of its input sequal to 1 and the third input connected dto I2. The other three AND gates have at least one input equal to 0, which makes their output sequal to 0. The OR output is now equal to the value of I2, providing a path from the selected in put to the output.

The data output is equal to IQ only if  $S_1 = 0$  and  $S_0 = 0$ ;

Y= I0S1'S0'.The data output is equal to I1 only if S1= 0 and S0= 1; Y= I1S1'S0.The data output is equal to I2 only if S1= 1 and S0= 0; Y= I2S1S0'.ThedataoutputisequaltoI3onlyifS1=1andS0=1;Y =I3S1S0.

When these terms are ORed, the total expression for the data output is,

#### Y=I0S1'S0'+I1S1'S0+I2S1S0'+I3S1S0.

As in decoder, multiplexers may have an enable input to control the operation of the unit. When the enable input is in the inactive state, the outputs are disabled, and when it is in the active state, the circuit functions as normal multiplexer.

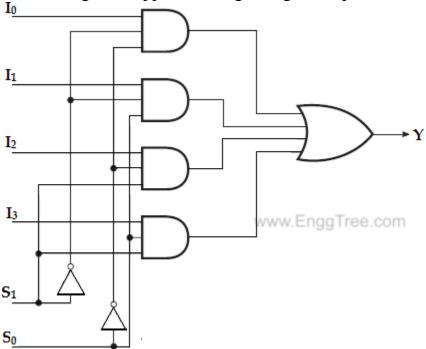

#### **<u>Quadruple 2-to-1LineMultiplexer:</u>**

www.EnggTree.com

PreparedByKAVIARASAN.S/Asst.Prof.,PIT

This circuit has four multiplexers, each capable of selecting one of two inputlines. Output Y0 can be selected to come from either A0 or B0. Similarly, output Y1 mayhave the value of A1 or B1, and so on. Input selection line, S selects one of the lines ineachofthefourmultiplexers. The enable input Emustbe active for normal operation.

Although the circuit contains four 2-to-1-Line multiplexers, it is viewed as acircuit that selects one of two 4-bit sets of data lines. The unit is enabled when E= 0.ThenifS=0,thefourAinputshaveapathtothefouroutputs.Ontheotherhand,ifS=1, the four B inputs are applied to the outputs. The outputs have all 0's when E= 1,regardlessofthevalueofS.

# Application:

ThemultiplexerisaveryusefulMSIfunctionandhasvariousrangesofapplicati ons in data communication. Signal routing and data communication are theimportantapplicationsofamultiplexer.Itisusedforconnectingtwoormoresource stoguide to a single destination among computer units and it is useful for constructing acommon bus system. One of the general properties of a multiplexer is that Booleanfunctionscanbeimplementedbythisdevice.

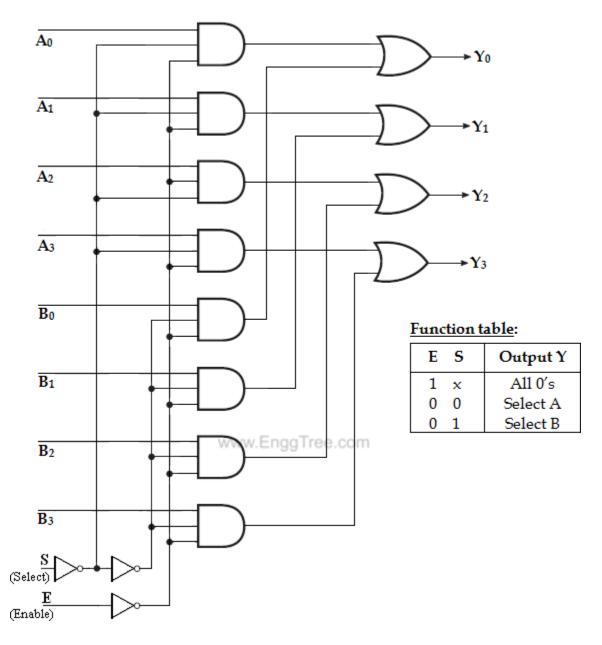

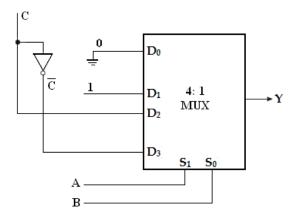

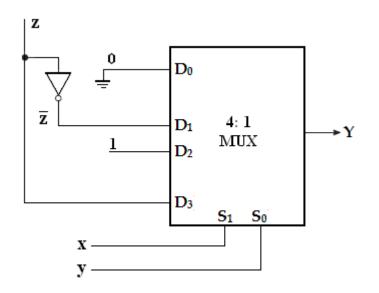

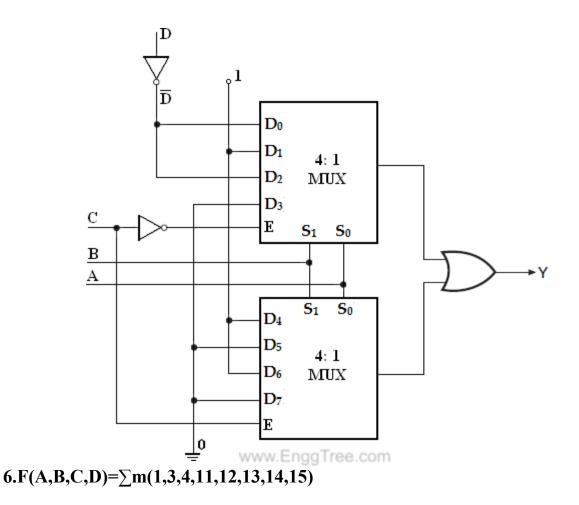

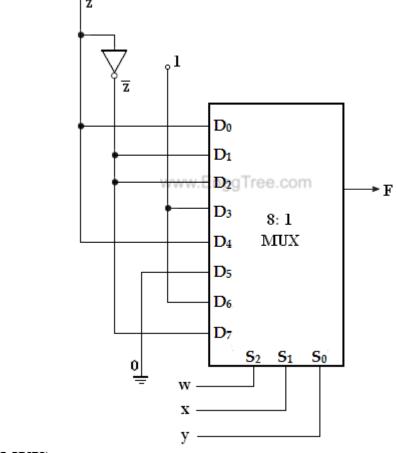

# ImplementationofBooleanFunctionusingMUX:

AnyBooleanorlogical expression can be easily implemented using a multiplex er. If a Boolean expression has (n+1) variables, then \_n' of these variables can be connected to the select lines of the multiplexer. The remaining single variable along with constants 1 and 0 is used as the input of the multiplexer. For example, if C is the single variable, then the input softhemultiplexers are C, C', 1 and 0. By this method a nylogical expression can be implemented.

In general, a Boolean expression of (n+1) variables can be implemented using amultiplexerwith  $2^n$  inputs.

# 1. Implementthefollowingboolean functionusing4:1multiplexer,F(A,B,C)=∑m(1,3,5,6). Solution:

Variables,n=3(A,B,C)Se lectlines=n-1=2(S1,S0)  $2^{n-1}$ toMUXi.e.,2<sup>2</sup>to1=4to1MUXInputli nes= $2^{n-1}=2^2=4$ (D0,D1,D2,D3)

# Implementationtable:

ApplyvariablesAandBtotheselectlines.Theproceduresforimplementingthefunct ionare:

- i. Listtheinputofthemultiplexer

- ii. Listunderthemallthemintermsintworowsasshownbelow.

The first half of the minterms is associated with A' and the second half with A. The given function is implemented by circling them interms of the function and apply ing the following rules to find the values for the inputs of the multiplexer.

1. If both them interms in the column are not circled apply 0 to the corresponding in Downloaded from Englinee.com

put.

- 2. If both them interms in the columnare circled, apply 1 to the corresponding input.

- 3. If the bottom mintermiscircled and the top is not circled, apply Ctothe input.

4. If the top mintermiscircle dand the bottom is not circled, apply C'to the input. <u>Multiple xer Implementation</u>:

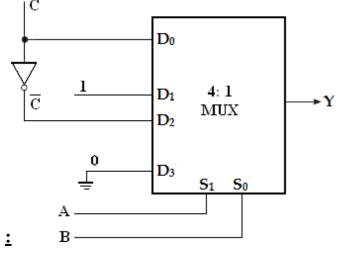

2.F(x,y,z)= $\sum m(1,2,6,7)$ Solution: Implementationtable:

|   | Do | D1 | <b>D</b> 2 | <b>D</b> 3 |

|---|----|----|------------|------------|

| ī | 0  | 1  | 2          | 3          |

| Z | 4  | 5  | 6          | $\bigcirc$ |

|   | 0  | z  | 1          | z          |

**Multiplexer Implementation:**

$3.F(A,B,C) = \sum m(1,2,4,5)$ <u>Solution:</u> Variables,n=3(A,B,C)Selectli

nes=n-1=2(**S1,S0**)

2**n-**

$1_{toMUXi.e.,2}$  to 1=4to 1MUXInputli nes= $2^{n-1}=2^2=4(\mathbf{D0,D1,D2,D3})$

# **Implementationtable:**

|   | Do | D1 | <b>D</b> <sub>2</sub> | <b>D</b> 3 |

|---|----|----|-----------------------|------------|

| C | 0  | 1  | 2                     | 3          |

| С | 4  | 6  | 6                     | 7          |

|   | С  | 1  | C                     | 0          |

# Multiplexer Implementation

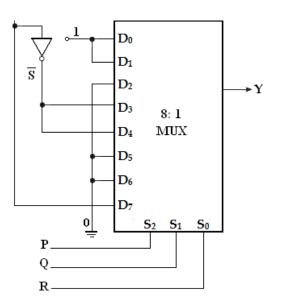

# $4.F(P,Q,R,S)=\sum m(0,1,3,4,8,9,15)$

### **Solution:**

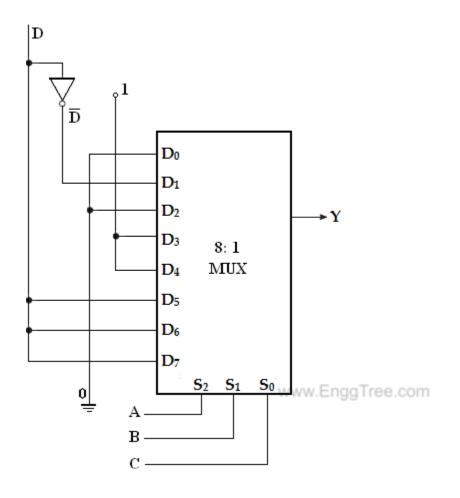

Variables,n=4(P,Q,R,S)Sel ectlines=n-1=3(**S2,S1,S0**)  $2^{n-1}$ toMUXi.e., $2^{3}$ to1=8to1MUX Inputlines= $2^{n-1}=2^{3}=8$ (**D0,D1,D2,D3,D4,D5,D6,D7**)

# **Implementationtable:**

|                         | Do | D1 | <b>D</b> 2 | <b>D</b> <sub>3</sub> | D <sub>4</sub> | <b>D</b> 5 | <b>D</b> 6 | <b>D</b> <sub>7</sub> |

|-------------------------|----|----|------------|-----------------------|----------------|------------|------------|-----------------------|

| $\overline{\mathbf{S}}$ | 0  | 1  | 2          | 3                     | 4              | 5          | 6          | 7                     |

| S                       | 8  | ٩  | 10         | 11                    | 12             | 13         | 14         | 15                    |

|                         | 1  | 1  | 0<br>0     | S                     | ee_co<br>S     | 0          | 0          | S                     |

**Multiplexer Implementation:**

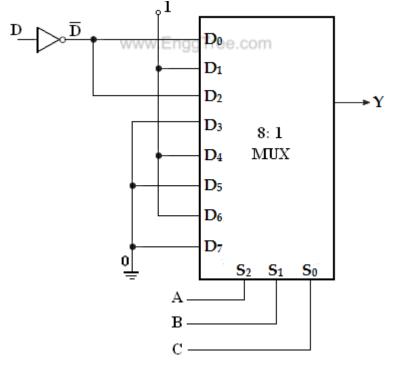

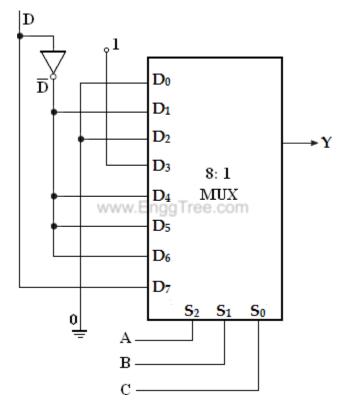

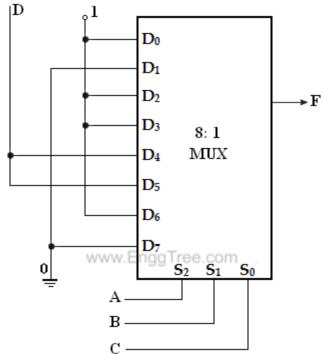

5. Implement the Boolean function using 8:1 and also using 4:1 multiplexer  $F(A,B,C,D) = \sum m(0,1,2,4,6,9,12,14)$ . Downloaded from EnggTree.com

# Solution:

Variables,n=4(A,B,C,D)Se lectlines=n-1=3(**S2,S1,S0**)  $2^{n-1}$ toMUXi.e., $2^{3}$ to1=8to1MUX Inputlines= $2^{n-1}=2^{3}=8$ (**D0,D1,D2,D3,D4,D5,D6,D7**)

|          |   | D <sub>0</sub>          | D1 | <b>D</b> <sub>2</sub>   | <b>D</b> <sub>3</sub> | D4   | D <sub>5</sub> | <b>D</b> 6 | <b>D</b> <sub>7</sub> |

|----------|---|-------------------------|----|-------------------------|-----------------------|------|----------------|------------|-----------------------|

|          | D | 0                       | 1  | 2                       | 3                     | 4    | 5              | ٩          | 7                     |

|          | D | 8                       | ٩  | 10                      | 11                    | (12) | 13             | (14)       | 15                    |

| ontable: |   | $\overline{\mathbf{D}}$ | 1  | $\overline{\mathbf{D}}$ | 0                     | 1    | 0              | 1          | 0                     |

Implementationtable:

MultiplexerImplementation(Using8:1MUX):

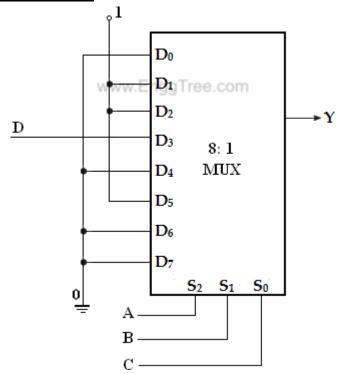

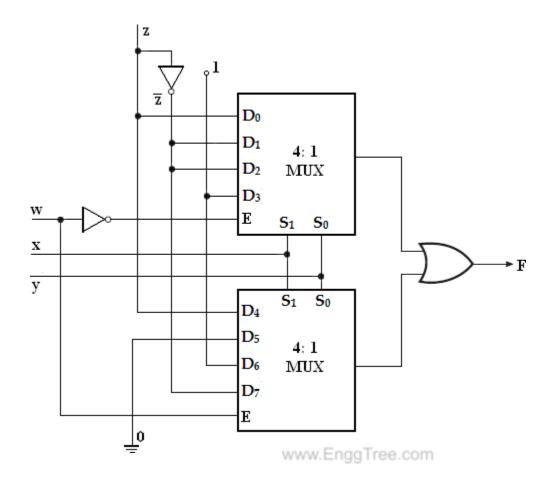

#### Using4:1MUX:

#### Solution:

Variables,n=4(A,B,C,D)Se lectlines=n-1=3(**S2,S1,S0**)  $2^{n-1}$ toMUXi.e., $2^{3}$ to1=8to1MUX Inputlines= $2^{n-1}=2^{3}=8$ (**D0,D1,D2,D3,D4,D5,D6,D7**)

Implementationtable:

|                         | Do | D1                      | <b>D</b> 2 | <b>D</b> 3 | $D_4$ | <b>D</b> 5 | <b>D</b> 6 | <b>D</b> <sub>7</sub> |

|-------------------------|----|-------------------------|------------|------------|-------|------------|------------|-----------------------|

| $\overline{\mathbf{D}}$ | 0  | 1                       | 2          | 3          | 4     | 5          | 6          | 7                     |

| D                       | 8  | 9                       | 10         | (11)       | (12)  | 13         | (14)       | (15)                  |

|                         | 0  | $\overline{\mathbf{D}}$ | 0          | 1          | 1     | D          | D          | D                     |

**Multiplexer Implementation:**

7. ImplementtheBooleanfunctionusing8:1multiplexer.

F(A,B,C,D)=A'BD'+ACD+B'CD+A'C'D.

# Solution:

ConvertintostandardSOPform,

$=A^{BD'}(C^{+}C)+ACD(B^{+}B)+B^{C}CD(A^{+}A)+A^{C}C^{D}(B^{+}B)$ =A^{BC'}D^{+}A^{B}CD^{+}AB^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{B}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^{C}^{C}CD+A^

# **Implementationtable:**

|                         | Do | D1                      | <b>D</b> 2 | <b>D</b> <sub>3</sub> | $D_4$                   | <b>D</b> 5              | <b>D</b> 6              | <b>D</b> 7 |

|-------------------------|----|-------------------------|------------|-----------------------|-------------------------|-------------------------|-------------------------|------------|

| $\overline{\mathbf{D}}$ | 0  | 1                       | 2          | 3                     | 4                       | 5                       | 6                       | 7          |

| D                       | 8  | 9                       | 10         | (11)                  | 12                      | 13                      | 14                      | (15)       |

|                         | 0  | $\overline{\mathbf{D}}$ | 0          | 1                     | $\overline{\mathbf{D}}$ | $\overline{\mathrm{D}}$ | $\overline{\mathbf{D}}$ | D          |

# **Multiplexer Implementation:**

# 8. ImplementtheBooleanfunctionusing8:1multiplexer. F(A,B,C,D)=AB'D+A'C'D+B'CD'+AC'D.

# Solution:

Convert into standard SOP form,

=AB'D(C'+C)+A'C'D(B'+B)+B'CD'(A'+A)+AC'D(B'+B)=<u>AB'C'D</u>+AB'CD+A'B'C'D+A'BC'D+A'B'CD'+AB'CD'+<u>AB'C</u> <u>'D</u>+ABC'D =AB'C'D+AB'CD+A'B'C'D+A'BC'D+A'B'CD'+AB'CD'+ABC' D =m9+m11+m1+m5+m2+m10+m13 = $\sum m (1,2,5,9,10,11,13).$

ImplementationTable:

|                         | Do | D1 | <b>D</b> 2 | <b>D</b> <sub>3</sub> | D4 | <b>D</b> 5 | D <sub>6</sub> | <b>D</b> 7 |

|-------------------------|----|----|------------|-----------------------|----|------------|----------------|------------|

| $\overline{\mathbf{D}}$ | 0  | 1  | 2          | 3                     | 4  | 6          | 6              | 7          |

| D                       | 8  | 9  | 10         | (11)                  | 12 | 13         | 14             | 15         |

|                         | 0  | 1  | 1          | D                     | 0  | 1          | 0              | 0          |

**Multiplexer Implementation:**

Implement the Boolean function using 8:1 and also using 4:1 multiplexer F(w,x,y,z)=∑m(1,2,3,6,7,8,11,12,14)

#### **Solution:**

Variables,n=4(w,x,y,z)Sele ctlines=n-1=3(S2,S1,S0)  $2^{n-1}$ toMUXi.e., $2^{3}$ to1=8to1MUX Inputlines= $2^{n-1}=2^{3}=8(D0,D1,D2,D3,D4,D5,D6,D7)$ Downloaded from EnggTree.com

Implementationtable:

|   | D <sub>0</sub> | <b>D</b> 1 | <b>D</b> <sub>2</sub> | $\mathbf{D}_3$ | $D_4$ | <b>D</b> 5 | <b>D</b> 6 | <b>D</b> <sub>7</sub> |

|---|----------------|------------|-----------------------|----------------|-------|------------|------------|-----------------------|

| Z | 0              | 1          | 2                     | 3              | 4     | 5          | (6)        | 1                     |

| Z | $(\infty)$     | 9          | 10                    | (11)           | (12)  | 13         | (14)       | 15                    |

|   | Z              | z          | z                     | 1              | z     | 0          | 1          | z                     |

# MultiplexerImplementation(Using8:1MUX):

(Using4:1MUX):

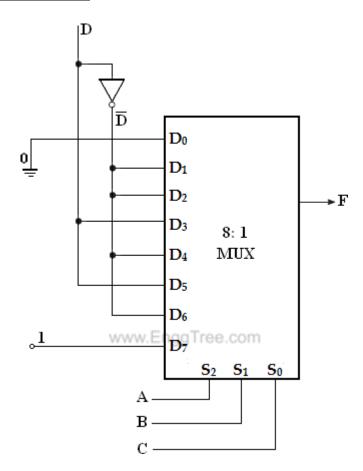

10. Implement the Boolean function using 8:1 multiplexer

$F(A,B,C,D) = \prod m(0,3,5,8,9,10,12,14)$ <u>Solution:</u>

Variables,n=4(A,B,C,D)Se lectlines=n-1=3(**S2,S1,S0**)  $2^{n-1}$ toMUXi.e., $2^{3}$ to1=8to1MUX Inputlines= $2^{n-1}=2^{3}=8$ (**D0,D1,D2,D3,D4,D5,D6,D7**)

# **Implementationtable:**

|   | Do | D1                      | <b>D</b> <sub>2</sub>   | <b>D</b> <sub>3</sub> | $D_4$                   | <b>D</b> 5 | <b>D</b> 6              | <b>D</b> 7 |

|---|----|-------------------------|-------------------------|-----------------------|-------------------------|------------|-------------------------|------------|

| D | 0  | 1                       | 2                       | 3                     | $(\mathbf{F})$          | 5          | 6                       | 3          |

| D | 8  | 9                       | 10                      | (11)                  | 12                      | 13         | 14                      | (15)       |

|   | 0  | $\overline{\mathrm{D}}$ | $\overline{\mathrm{D}}$ | D                     | $\overline{\mathbf{D}}$ | D          | $\overline{\mathrm{D}}$ | 1          |

**Multiplexer Implementation:**

# 11. Implement the Boolean function using 8:1 multiplexer $F(A,B,C,D) = \sum m(0,2,6,10,11,12,13) + d(3,8,14)$ <u>Solution:</u>

# Variables,n=4(A,B,C,D)Se lectlines=n-1=3(**S2,S1,S0**) $2^{n-1}$ toMUXi.e., $2^{3}$ to1=8to1MUX Inputlines= $2^{n-1}=2^{3}=8($ **D0,D1,D2,D3,D4,D5,D6,D7**)

#### **ImplementationTable:**

|   | Do         | D1 | <b>D</b> 2 | <b>D</b> <sub>3</sub> | D <sub>4</sub> | <b>D</b> 5 | <b>D</b> 6 | <b>D</b> 7 |

|---|------------|----|------------|-----------------------|----------------|------------|------------|------------|

| D | 0          | 1  | 2          | 3                     | 4              | 5          | ٩          | 7          |

| D | $(\infty)$ | 9  | 10         | (11)                  | (12)           | 13         | (14)       | 15         |

|   | 1          | 0  | 1          | 1                     | D              | D          | 1          | 0          |

**Multiplexer Implementation:**

12. An8×1multiplexer hasinputsA,BandC

connected to these lection inputs S2, S1, and S0 respectively. The data inputs I0 to I7 are as follows

I1=I2=I7=0;I3=I5=1;I0=I4=DandI6=D'.

Determine the Boolean function that the multiple xerimplements.

# **Multiplexer Implementation:**

www.EnggTree.com

# **Implementationtable:**

|                         | , <b>I</b> 0, | Iı | -4 | ->   | -4   | -7 | <b>~</b> 0 .            | ~, |

|-------------------------|---------------|----|----|------|------|----|-------------------------|----|

| $\overline{\mathbf{D}}$ | 0             | 1  | 2  | 3    | 4    | 5  | ٩                       | 7  |

| D                       | 8             | 9  | 10 | (11) | (12) | 13 | 14                      | 15 |

|                         | D             | 0  | 0  | 1    | D    | 1  | $\overline{\mathrm{D}}$ | 0  |

$F(A,B,C,D)=\sum m(3,5,6,8,11,12,13).$

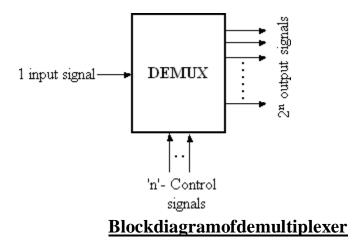

# **DEMULTIPLEXER:**

Demultiple x means one into many. Demultiple x ingis the process of taking information from one input and transmitting the same over one of several outputs.

$\label{eq:ademultiplexer} A demultiplexer is a combinational logic circuit that receives information on a simulation of the same information over one of several (2^n) output lines.$

The block diagram of a demultiplexer which is opposite to a multiplexer in its shown above. The circuit has one input signal, \_n' select signals and  $2^{n}$  output signals. The select inputs determine to which output the data input will beconnected. As the serial data is changed to parallel data, i.e., the input caused to appearononeofthenoutputlines, the demultiplexer is also called a *data distributer* ora --serial-to-parallel converter .

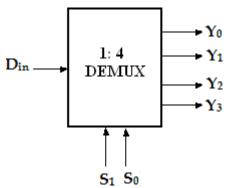

**<u>1-to-4Demultiplexer:</u>**

A1-to-

4demultiplexerhasasingleinput, **Din**, fouroutputs(**Y0toY3**) and two selectinputs(**S** 1and **S0**).

**LogicSymbol**

The input variable Dinhas a path to all four outputs, but the input information is directed to only one of the output lines. The truth table of the 1-to-4 demultiplexer is shown below.

| Enabl | <b>S1</b> | S0     | Din       | Y0      | Y1  | Y2 | <b>Y3</b> |

|-------|-----------|--------|-----------|---------|-----|----|-----------|

| e     |           |        |           |         |     |    |           |

| 0     | Х         | Х      | Х         | 0       | 0   | 0  | 0         |

| 1     | 0         | 0      | 0         | 0       | 0   | 0  | 0         |

| 1     | 0         | 0      | 1         | 1       | 0   | 0  | 0         |

| 1     | 0         | 1      | 0         | 0       | 0   | 0  | 0         |

| 1     | 0         | 1      | 1         | 0       | 1   | 0  | 0         |

| 1     | 1         | 0      | 0         | 0       | 0   | 0  | 0         |

| 1     | 1         | 0      | 1         | 0       | 0   | 1  | 0         |

| 1     | 1         | 1      | 0         | 0       | 0   | 0  | 0         |

| 1     | 1         | 1      | 1         | 0       | 0   | 0  | 1         |

|       | Trutht    | ableof | 1-to-4dem | ultiple | xer | •  | •         |

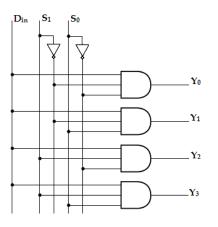

Fromthetruthtable, it is clear that the data input, Dinisconnected to the output Y0, when  $S_{1}=0$  and  $S_{0}=0$  and the data input is connected to output Y1 when  $S_{1}=0$  and  $S_{0}=1$ . Similarly, the data input is connected to output Y2 and Y3 when  $S_{1}=1$  and  $S_{0}=0$  and when  $S_{1}=1$  and  $S_{0}=1$ , respectively. Also, from the truth table, the expression for output scanbe written as follows,

Y0=

S1'S0'DinY1=

S1'S0DinY2=S1S0

'Din

Y3=S1S0Din

Logicdiagramof1-to-4demultiplexer Downloaded from EnggTree.com

Now, using the above expressions, a 1-to-4 demultiplexer can be implementedusingfour3-inputAND gatesand twoNOT gates. Here,theinputdatalineDin,isconnectedto allthe ANDgates.ThetwoselectlinesS1,S0enableonlyonegate at a time.andthedatathatappearsontheinputlinepassesthroughtheselectedgatetotheassoci atedoutputline.

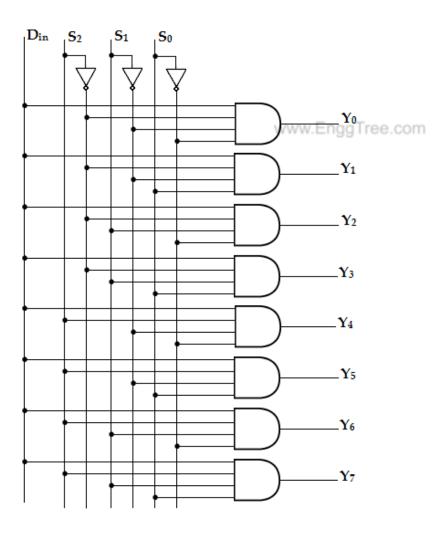

#### **<u>1-to-8Demultiplexer:</u>**

A1-to-

8 demultiple xerhas a single input, Din, eight outputs (Y0 to Y7) and three select inputs (S2, S1 and S0). It distributes one input line to eight output lines based on the select inputs . The truth table of 1-to-8 demultiple xeris shown below.

| Din | S<br>2 | <b>S</b> 1 | S0 | Y<br>7 | Y<br>6 | Y<br>ee 5on | Y<br>4 | Y<br>3 | Y<br>2 | Y<br>1 | Y<br>0 |

|-----|--------|------------|----|--------|--------|-------------|--------|--------|--------|--------|--------|

| 0   | X      | X          | Х  | 0      | 0      | 0           | 0      | 0      | 0      | 0      | 0      |

| 1   | 0      | 0          | 0  | 0      | 0      | 0           | 0      | 0      | 0      | 0      | 1      |

| 1   | 0      | 0          | 1  | 0      | 0      | 0           | 0      | 0      | 0      | 1      | 0      |

| 1   | 0      | 1          | 0  | 0      | 0      | 0           | 0      | 0      | 1      | 0      | 0      |

| 1   | 0      | 1          | 1  | 0      | 0      | 0           | 0      | 1      | 0      | 0      | 0      |

| 1   | 1      | 0          | 0  | 0      | 0      | 0           | 1      | 0      | 0      | 0      | 0      |

| 1   | 1      | 0          | 1  | 0      | 0      | 1           | 0      | 0      | 0      | 0      | 0      |

| 1   | 1      | 1          | 0  | 0      | 1      | 0           | 0      | 0      | 0      | 0      | 0      |

| 1   | 1      | 1          | 1  | 1      | 0      | 0           | 0      | 0      | 0      | 0      | 0      |

# Truthtableof1-to-8demultiplexer

$\label{eq:Fromtheabovetruthtable, it is clear that the data input is connected with one of the eight outputs based on the select inputs. Now from this truthtable, the expression for eight outputs can be written as follows:$

Y0=S2'S1'S0'Din

Y1=S2'S1'S0Din

Y2=S2'S1S0'Din

Y3=S2'S1S0Din

Y4= S2S1'S0'Din

Y5=S2S1'S0DiDownloaded from EnggTree.com

Y6= S2S1S0'Din

Y7=S2S1S0Din

Now using the above expressions, the logic diagram of a 1-to-8 demultiplexer can bedrawn as shown below. Here, the single data line, Din is connected to all the eight ANDgates, but only one of the eight AND gates will be enabled by the select input lines. Forexample, if S2S1S0= 000, then only AND gate-0 will be enabled and thereby the datainput,DinwillappearatY0.Similarly,thedifferentcombinationsoftheselectinp uts,theinputDinwillappearattherespectiveoutput.

Logicdiagramof1-to-8demultiplexer

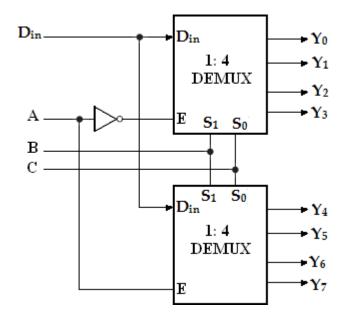

<sup>1.</sup> Design1:8demultiplexerusingtwo1:4DEMUX.

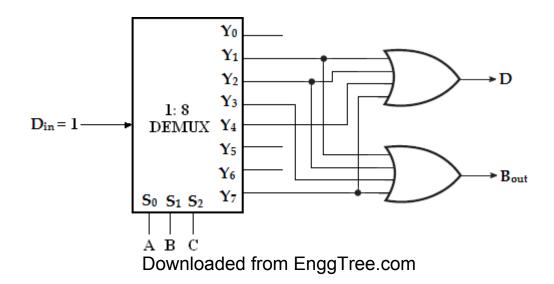

2. Implementfullsubtractorusingdemultiplexer.

|   | Input<br>s |                  | Output<br>s  |           |  |

|---|------------|------------------|--------------|-----------|--|

| Α | В          | ww <b>Bi</b> Eng | Difference(D | Borrow(Bo |  |

|   |            | n                | )            | ut)       |  |

| 0 | 0          | 0                | 0            | 0         |  |

| 0 | 0          | 1                | 1            | 1         |  |

| 0 | 1          | 0                | 1            | 1         |  |

| 0 | 1          | 1                | 0            | 1         |  |

| 1 | 0          | 0                | 1            | 0         |  |

| 1 | 0          | 1                | 0            | 0         |  |

| 1 | 1          | 0                | 0            | 0         |  |

| 1 | 1          | 1                | 1            | 1         |  |

#### EnggTree.com UNITII-SYNCHRONOUS SEQUENTIAL LOGIC

#### INTRODUCTION

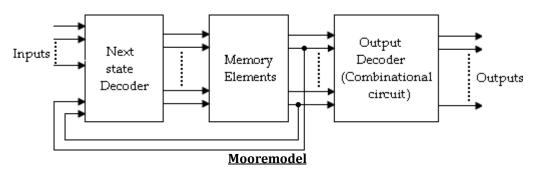

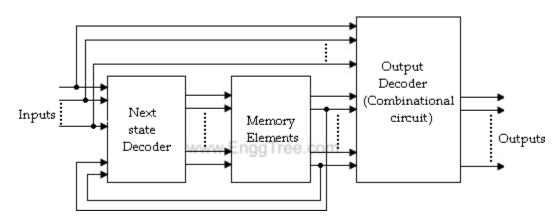

$In {\it combinational logic circuits}, the outputs at any instant of time depend only on the input signal spresent at that time. For a change in input, the output occurs immediately.$

In *sequential logic circuits*, it consists of combinational circuits to whichstorage elements are connected to form a feedback path. The storage elements aredevicescapableofstoringbinaryinformationeither1or0.

The information stored in the memory elements at any given time defines the present state of these quential circuit. The present state and the external circuit determine the output and the next state of sequential circuits.

SequentialCircuit-BlockDiagram

www.EnggTree.com

Thusinsequential circuits, the output variables depend not only on the present input variables but also on the past history of input variables.

Therotarychannelselectedknobonanold-fashionedTVislikeacombinational. Its output selects a channel based only on its current input – theposition of the knob. The channel-up and channel-down push buttons on a TV is likeasequentialcircuit.Thechannelselectiondependsonthepastsequenceofup/downpus hes.Thecomparisonbetweencombinationalandsequentialcircuitsisgivenintablebelow.

| S.No | Combinationallogic                                                           | Sequentiallogic                                                                                  |

|------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| 1    | Theoutputvariable,atalltimesd<br>ependsonthecombinationof<br>inputvariables. | Theoutputvariabledependsnotonlyo<br>nthepresentinputbutalsodepend<br>uponthepasthistoryofinputs. |

| 2    | Memoryunitisnotrequired                                                      | Memoryunitisrequiredtostorethe pasthistoryofinputvariables.                                      |

| 3    | Fasterinspeed                                                                | Slowerthancombinationalcircuits.                                                                 |

| 4    | Easy to design                                                               | Comparativelyhardertodesign.                                                                     |

| 5    | Eg.Paralleladder                                                             | Eg.Serialadder                                                                                   |

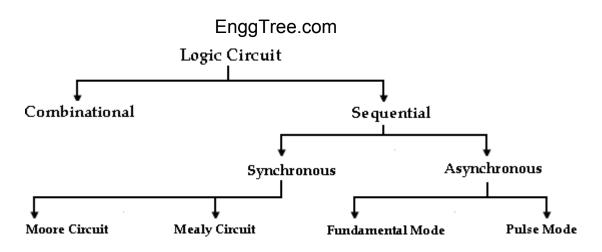

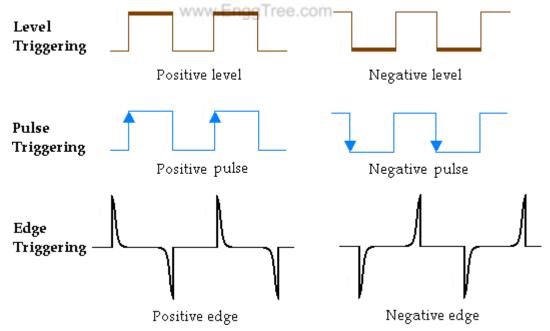

The sequential circuits can be classified depending on the timing of their signals:

- Synchronoussequentialcircuits

- Asynchronoussequentialcircuits.

In synchronous sequential circuits, signals can affect the memory elementsonlyatdiscreteinstantsoftime.Inasynchronoussequentialcircuitschange ininput signals can affect memory element at any instant of time. The memoryelements used in both circuits are Flip-Flops, which are capable of storing 1-bitinformation.

| S.No | Synchronoussequentialcircuits                                                           | Asynchronoussequentialcircuits                                                   |  |  |

|------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| 1    | Memoryelements are clocked<br>Flip-Flops                                                | Memoryelementsareeitherunclocked<br>Flip-Flopsortimedelayelements.               |  |  |

| 2    | Thechangeininputsignalscan<br>affect memory element<br>uponactivationofclocksig<br>nal. | Thechangeininputsignalscanaffectmem<br>oryelementatanyinstantoftime.             |  |  |

| 3    | Themaximumoperatingspeedofc<br>lockdependsontimedelays<br>involved.                     | Becauseoftheabsenceofclock,itcanoper<br>ate faster than synchronous<br>circuits. |  |  |

| 4    | Easiertodesign                                                                          | Moredifficulttodesign                                                            |  |  |

# LATCHES:

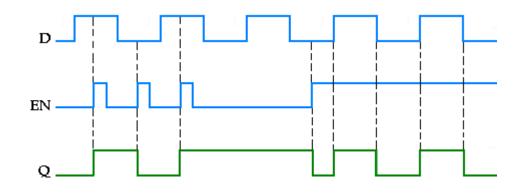

Latches and Flip-Flops are the basic building blocks of the most sequentialcircuits.Latchesareusedforasequentialdevicethatchecksallofitsinputscontinu ouslyandchangesitsoutputsaccordinglyatanytimeindependentofclockingsignal.Enables ignalisprovidedwiththelatch.Whenenablesignal isactive output changes occur as the input changes. But when enable signal is notactivatedinputchangesdonotaffecttheoutput.

Flip-Flop is used for a sequential device that normally samples its inputs andchangesitsoutputsonlyattimesdeterminedbyclockingsignal.

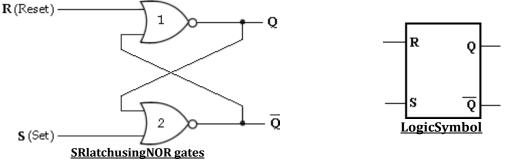

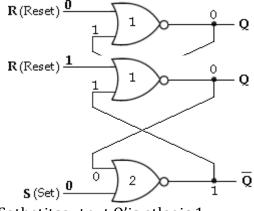

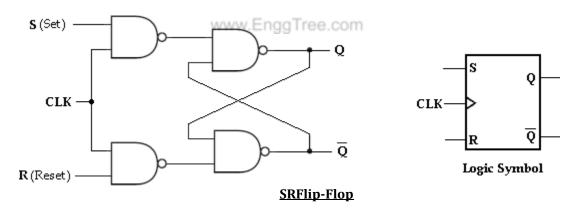

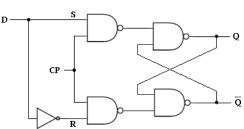

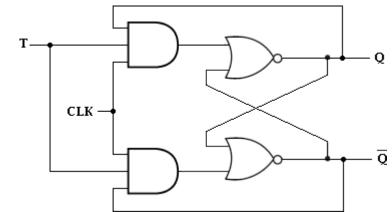

#### SRLatch:

The simplest type of latch is the set-reset (SR) latch. It can be constructed from thertwo NORga to the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set-reset (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It can be constructed from the set (SR) latch. It

#### SRlatchusingNORgates:

The two NOR gates are cross-coupled so that the output of NOR gate 1 is connected to one of the inputs of NOR gate 2 and vice versa. The latch has twooutputsQandQ'andtwoinputs, setandreset.

Before going to analyse the SR latch, we recall that a logic 1 at any input of aNORgateforcesitsoutputtoalogic0.Letusunderstandtheoperationofthiscircuitforvariou sinput/outputpossibilities.

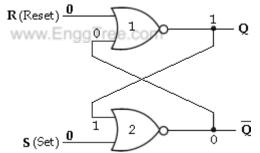

#### Case1:S=0andR=0

Initially,Q=1andQ'=0

Letus assume that initially Q=1 and Q'=0. With Q'=0, both inputs to NOR gate 1 are at logic 0. So, its output, Q is at logic 1. With Q=1, one input of NOR gate 2 is at logic

1. Hence its output, Q' is at logic 0. This shows that when S and R both arelow, the output does not change.

Initially, Q=0 and Q'=1

WithQ'=1,oneinputofNORgate1isatlogic1,henceitsoutput,Qisatlogic 0.WithQ=0,bothinputstoNORgate2areatlogic

$0. So, its output Q' is at logic 1. In this case also there is no change in the output state. \\ Case 2: S=0 and R=1$

In this case, Rinput of the NOR gate 1 is at logic 1, hence its output, Q is at logic 0. Both inputs to NO the second s

Rgate2arenowatlogic 0.Sothatitsoutput,Q'is atlogic 1.

#### EnggTree.com toNORgate1arenow atlogic0.Sothatits output,Qisatlogic 1.

#### Case4:S=1andR=1

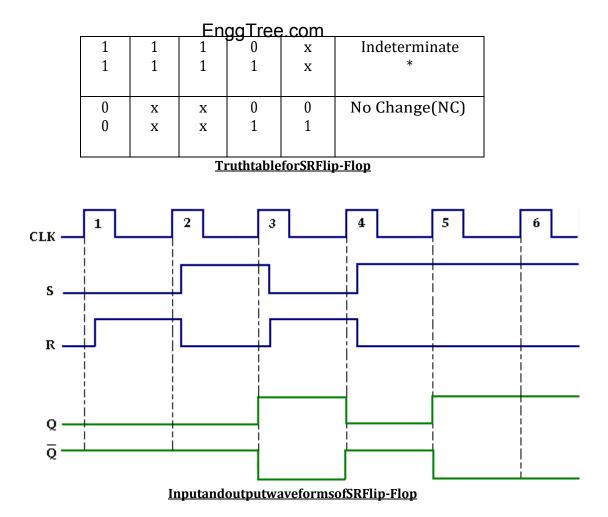

When R and S both are at logic 1, they force the outputs of both NOR gates to the low state, i.e., (Q=0 and Q'=0). So, we call this an indeterminate or prohibited state, and represent this condition in the truth table as an asterisk (\*). This condition nalso violates the basic definition of a latch that requires Q to be complement of Q'. Thus innormal operation this condition must be avoided by making sure that 1's are not applied to both the inputs simultaneously.

We can summarize the operation of SR latch as follows:

- WhenS=0andR= 0,theoutput, Q<sub>n+1</sub>remainsinitspresentstate,Q<sub>n</sub>.

- WhenS=0andR=1,thelatchisresetto0.

- WhenS=1andR=0,thelatchissetto1.

- WhenS=1andR=1,theoutputofbothgateswillproduce0.i.e.,  $Q_{n+1} = Q_{n+1}'=0$ .

| S | R    | Qn     | Q <sub>n+1</sub> | State         |

|---|------|--------|------------------|---------------|

| 0 | 0    | 0      | 0                | No Change     |

| 0 | 0    | 1      | 1                | (NC)          |

|   | M040 | v Enga | Free co          | m             |

| 0 | 1    | 0      | 0                | Reset         |

| 0 | 1    | 1      | 0                |               |

|   |      |        |                  |               |

| 1 | 0    | 0      | 1                | Set           |

| 1 | 0    | 1      | 1                |               |

|   |      |        |                  |               |

| 1 | 1    | 0      | Х                | Indeterminate |

| 1 | 1    | 1      | Х                | *             |

|   |      |        |                  |               |

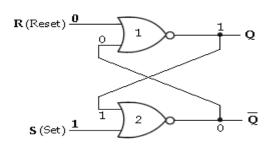

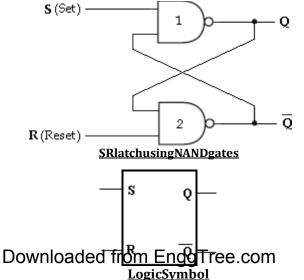

#### SRlatchusingNANDgates:

The SR latch can also be implemented using NAND gates. The inputs of this Latch are Sand R. To understand how this circuit functions, recall that allow on any input to a NAND gate for cesits output high.

EnggTree.com WecansummarizetheoperationofSRIatchasfollows:

- WhenS=0andR=0,theoutputofboth gateswillproduce0.i.e.,**Q**<sub>n+1</sub>=**Q**<sub>n+1</sub>'=1.

- WhenS=0andR=1,thelatchisresetto0. •

- WhenS=1andR=0,thelatchissetto1. •

- WhenS=1andR= 1,theoutput, Q<sub>n+1</sub>remainsinitspresentstate,Q<sub>n</sub>.

| S | R | Qn | Q <sub>n+1</sub> | State         |

|---|---|----|------------------|---------------|

| 0 | 0 | 0  | Х                | Indeterminate |

| 0 | 0 | 1  | х                | *             |

|   |   |    |                  |               |

| 0 | 1 | 0  | 1                | Set           |

| 0 | 1 | 1  | 1                |               |

|   |   |    |                  |               |

| 1 | 0 | 0  | 0                | Reset         |

| 1 | 0 | 1  | 0                |               |

|   |   |    |                  |               |

| 1 | 1 | 0  | 0                | No Change     |

| 1 | 1 | 1  | 1                | (NC)          |

|   |   |    |                  |               |

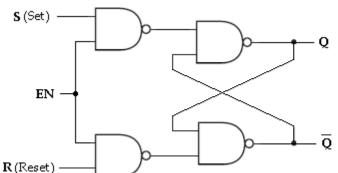

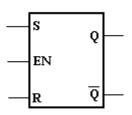

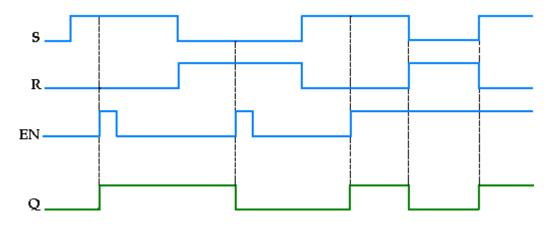

#### **GatedSRLatch:**

IntheSRlatch,theoutputchangesoccurimmediatelyaftertheinputchangesi.e,thela tchissensitivetoitsSandRinputsallthetime.

Alatchthatissensitivetotheinputsonlywhenanenableinputisactive.Suchalatchwithena bleinputisknownasgatedSRlatch.

$The circuit behaves like SR latch when {\tt EN=1.} It retains its previous state when {\tt EN=1.} It retains its$ • =0

**LogicSymbol**

ThetruthtableofgatedSRlatchisshowbelow.

| EN | S      | R     | Qn       | Q <sub>n+1</sub> | State         |

|----|--------|-------|----------|------------------|---------------|

| 1  | 0      | 0     | 0        | 0                | No Change(NC) |

| 1  | 0      | 0     | 1        | 1                |               |

|    |        |       |          |                  |               |

| 1  | 0      | 1     | 0        | 0                | Reset         |

| 1  | 0      | 1     | 1        | 0                |               |

|    |        |       |          |                  |               |

| 1  | 1      | 0     | 0        | 1                | Set           |

| 1  | 1      | 0     | 1        | 1                |               |

|    |        |       |          |                  |               |

| 1  | 1      | 1     | 0        | Х                | Indeterminate |

| 1  | Do∲vnl | oadec | l frðm l | EnğgTı           | ree.com *     |

| EngaTree.com |   |   |   |   |               |  |  |  |

|--------------|---|---|---|---|---------------|--|--|--|

| 0            | Х | Х | 0 | 0 | No Change(NC) |  |  |  |

| 0            | Х | х | 1 | 1 |               |  |  |  |

|              |   |   |   |   |               |  |  |  |

When Sis HIGH and Ris LOW, a HIGH on the EN input sets the latch. When Sis LOW and Ris HIGH, a HIGH on the EN input resets the latch.

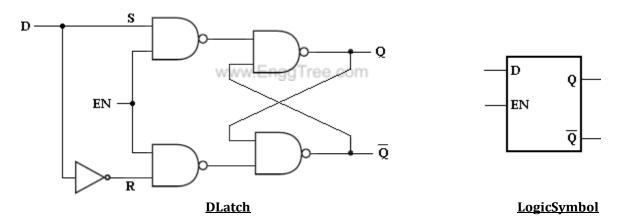

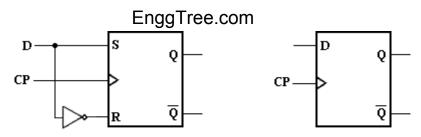

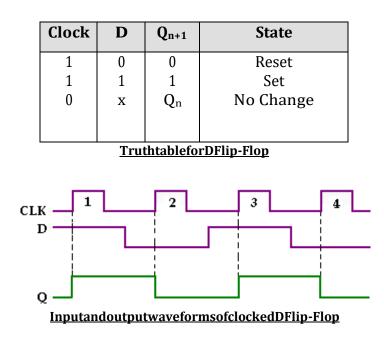

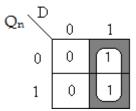

#### **DLatch**

In SR latch, when both inputs are same (00 or 11), the output either does notchange or it is invalid. In many practical applications, these input conditions are notrequired. These input conditions can be avoided by making them complement ofeachother.ThismodifiedSRlatchisknownas**Dlatch**.

Asshowninthefigure,DinputgoesdirectlytotheSinput,anditscomplement is applied to the R input. Therefore, only two input conditions exists,eitherS=0andR=1orS=1andR=0.The truthtableforDlatchisshownbelow.

| EN | D | Qn | Q <sub>n+1</sub> | State         |

|----|---|----|------------------|---------------|

| 1  | 0 | Х  | 0                | Reset         |

| 1  | 1 | Х  | 1                | Set           |

| 0  | х | х  | $Q_n$            | No Change(NC) |

|    |   |    |                  |               |

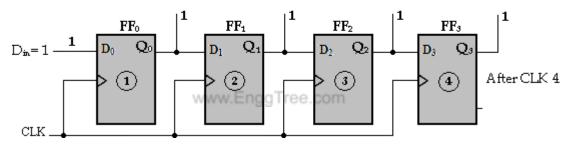

$\label{eq:asshown} As shown in the truth table, the Qoutput follows the Dinput. For this reason, Dlatchis called transparent latch.$